em có bài tập thế này :

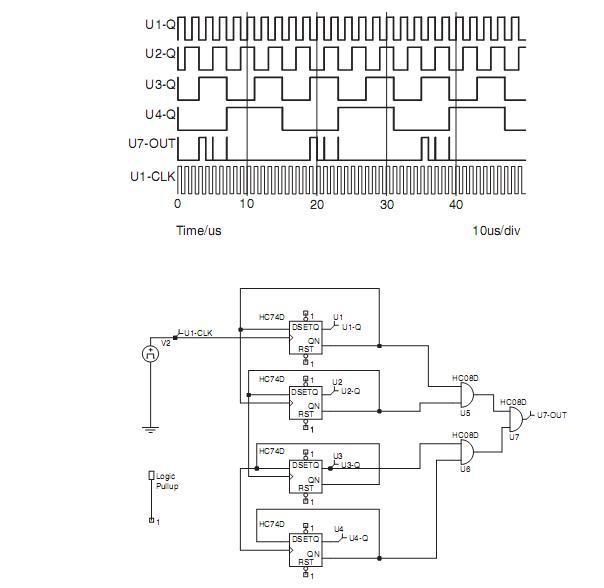

mạch đếm không đồng bộ đếm lên đếm 5 dùng 3 T.FF , đếm từ 000 , 001 , 010 , 011 , 100 rồi quay về 000 .

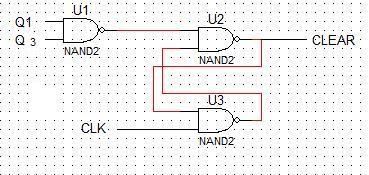

Cách xử lý ban đầu là cho nó đếm đến 100 , sang 101 thì xuất clear = NAND (Q1,Q3) để xóa các FF về 0 .

Tuy nhiên cách này có nhược điểm là clear ngắn nên có thể không xóa hết 3 FF , thay vì 000 ta có thể có 001 hoặc 100 => sai .

Yêu cầu là sửa lại mạch , kèm clock vào hàm clear để kéo dài clear đến 1/2 chu kỳ .

Em nghĩ nát óc rồi mà không tìm ra cách nào để clear kéo dài 1/2 chu kỳ clock mà vẫn không ảnh hưởng đến mạch đếm

Xin các cao thủ ra tay trợ giúp . Em cảm ơn nhiều nhiều .

mạch đếm không đồng bộ đếm lên đếm 5 dùng 3 T.FF , đếm từ 000 , 001 , 010 , 011 , 100 rồi quay về 000 .

Cách xử lý ban đầu là cho nó đếm đến 100 , sang 101 thì xuất clear = NAND (Q1,Q3) để xóa các FF về 0 .

Tuy nhiên cách này có nhược điểm là clear ngắn nên có thể không xóa hết 3 FF , thay vì 000 ta có thể có 001 hoặc 100 => sai .

Yêu cầu là sửa lại mạch , kèm clock vào hàm clear để kéo dài clear đến 1/2 chu kỳ .

Em nghĩ nát óc rồi mà không tìm ra cách nào để clear kéo dài 1/2 chu kỳ clock mà vẫn không ảnh hưởng đến mạch đếm

Xin các cao thủ ra tay trợ giúp . Em cảm ơn nhiều nhiều .

...

...

Comment