* Yêu cầu :

+ Có kiến thức về Hệ thống, kiến trúc máy tính.

+ Biết sử dụng Altera Quartus + SoPC Builder hoặc Xilinx ISE + BSB + XPS

Mặc dù với FPGA ,ta phải xây dựng một một thống từ cổng logic/IC số. Nhưng thực tế không đến nỗi bi đát như vậy. Các nhà sản xuất FPGA cung cấp cho chúng ta các công cụ xây dựng hệ thống cực nhanh (Altera có SoPC Builder, Xilinx có BSB). Thực chất là người ta xây dựng sẵn các thư viện module (khối làm chức năng nào đó) gọi là IP (Intellectual Property) , là sở hữu trí tuệ của những người đã làm ra nó.Vì hệ thống thường có những khối giống nhau, hơn nữa đôi khi chúng ta chỉ muốn phát triển một chức năng nào đó (vd một chip điều khiển PID chằng hạn), trong khi không muốn tốn thời gian thiết kế tòan bộ hệ thống, mà Chip thiết kế ra thì cần phải được đặt trong một hệ thống để có thể hoạt động được. Tuy nhiên nếu bạn muốn bao gồm các IP này trong thiết kế (vd thiết kế của bạn cần 1 IP của các công ty nào đó thì bạn phải lưu ý về bản quyền của IP đó). Thông thường các IP được cung cấp cho chúng ta dùng thử ở dạng mã hóa (bạn không thể nhìn thấy kiến trúc của nó), bạn có thể tạm thời sử dụng chúng cho thiết kế của mình mà không quan tâm đến nội dung bên trong.

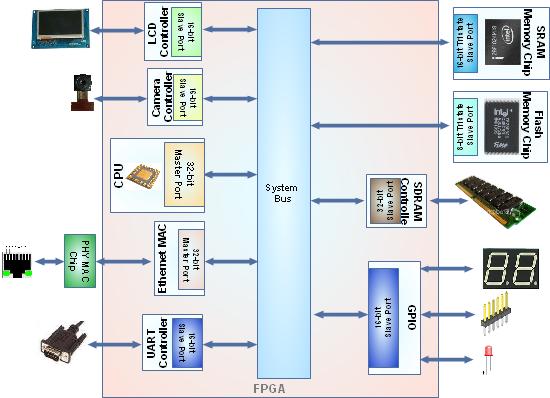

Các FPGA vendor hoặc các công ty thứ 3 đều có hầu như đầy đủ tất cả các IP cần thiết cho bạn phát triển hệ thống vd như CPU Core, Timer, UART, JTAG, Memory, DMA controller, Ethernet, USB, SPI, I2C …Sau đây là một ví dụ về một hệ thống hoàn chỉnh

Vấn đề là ta cần một hệ thống BUS để kết nối tất cả nhưng module này lại để hệ thống có thể hoạt động tốt, điều này tưởng chừng như là một vấn đề đơn giản của hệ thống, nhưng thực ra hệ thống bus rất quan trọng và gây ra nhiều vấn đề cho toàn bộ hệ thống vd như chia sẻ băng thông, tốc độ hệ thống …Đôi khi chính hệ thống bus quyết định cả hiệu quả của toàn hệ thống. Nhưng dù sao đi nữa Altera và Xilinx cũng đã giúp ta phần lớn công việc xây dựng system bus bằng các công cụ chuyên dụng. Ở đây mình giới thiệu tổng quan cả hai công cụ của xilinx và altera :

* Altera SoPC Builder (System On Programmable Chip)

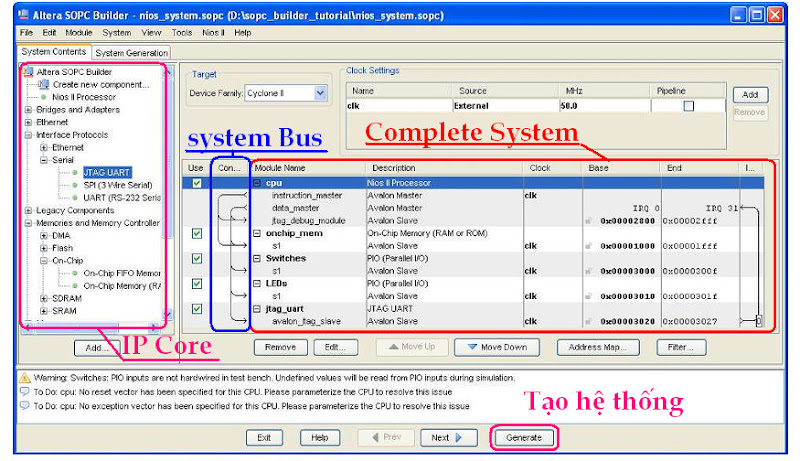

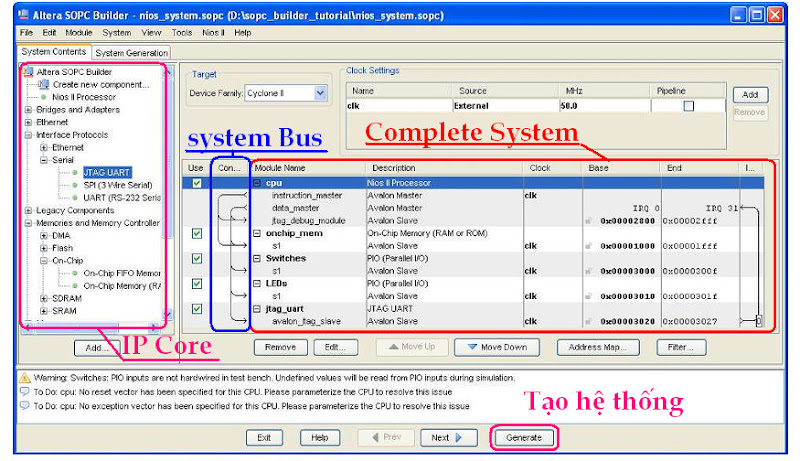

Giao diện tạo hệ thống của Altera (SOPC Builder)

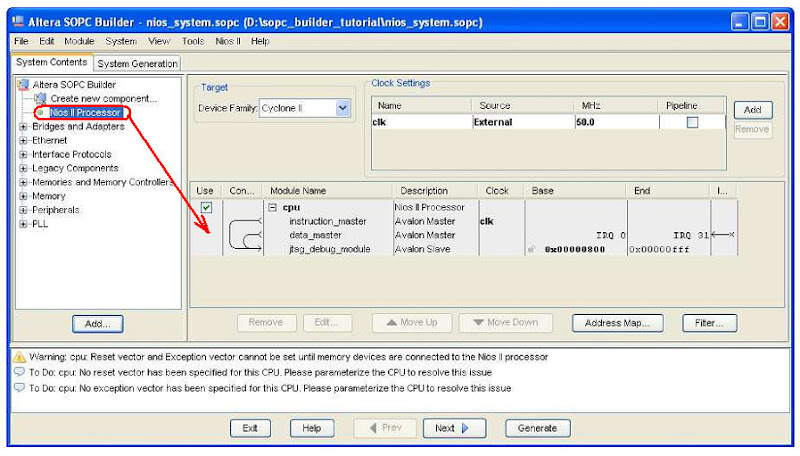

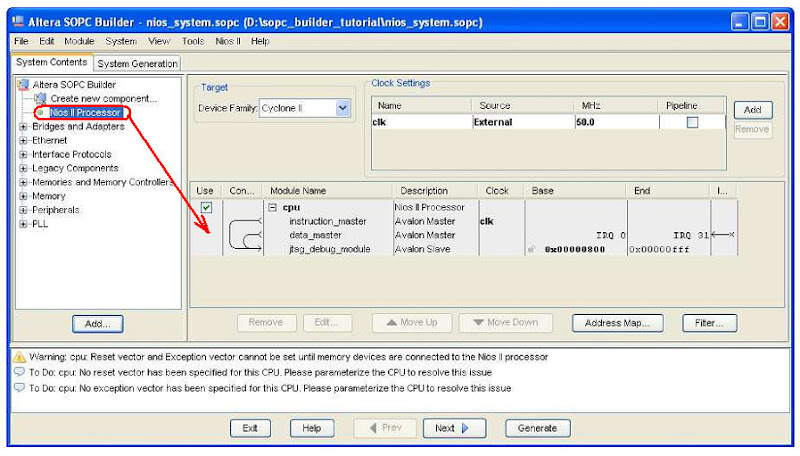

Chọn CPU vào hệ thống (Mình bỏ qua việc chọn các thông số cho đơn giản nha)

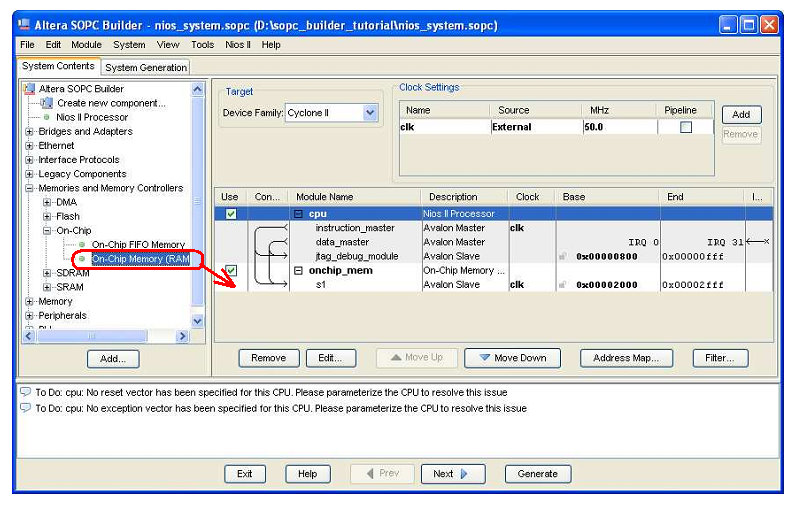

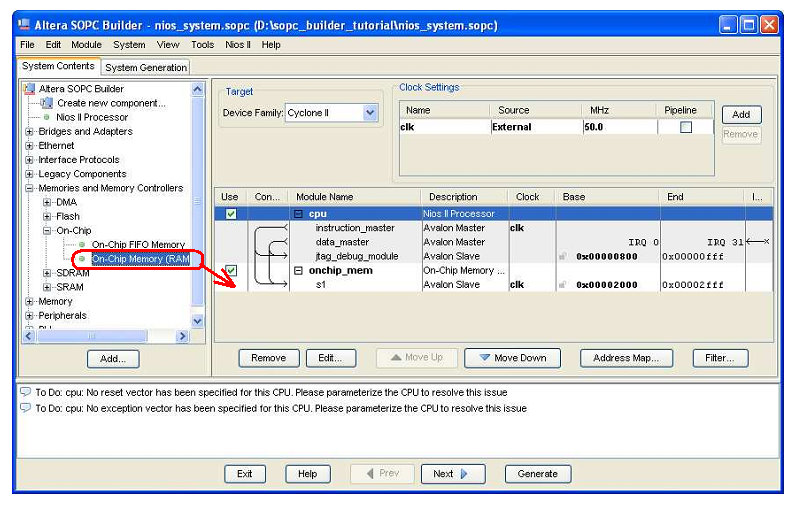

Thêm Bộ nhớ Cho CPU hoạt động nè (CPU phải có bộ nhớ onChip để chứa Instruction và Data)

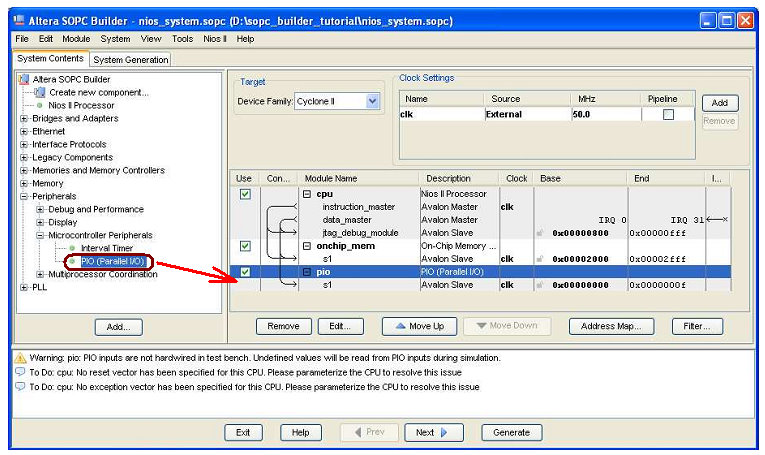

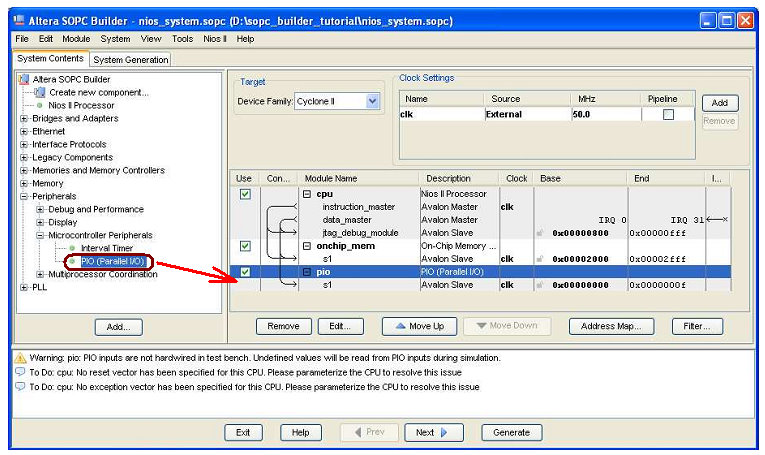

Thêm PIO (Parallel Input/Output) cho hệ thống (tức là các Port I/O đa năng ấy mà)

Thêm LED,UART cho thành hệ thống hoàn chỉnh. Chú ý là bạn phải chọn các kết nối cho system connect bus, nếu không CPU sẽ không thể giao tiếp được với các ngoại vi

Bây giờ nhấn nút cái là thành một cái hệ thống hoàn chỉnh, tất cả chỉ mất vài phút cho các hệ thống không quá phức tạp

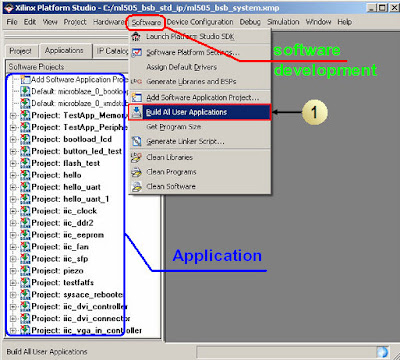

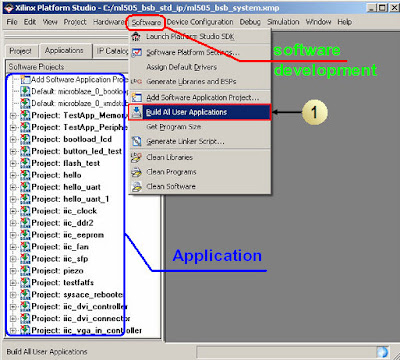

* Xilinx BSB (Base System Builder) và XPS (Xilinx Platform Studio)

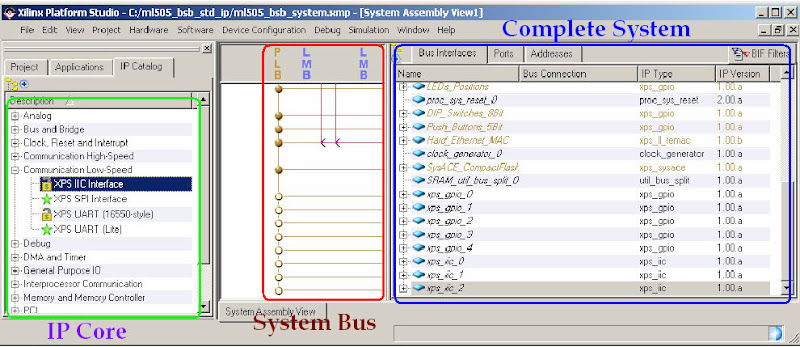

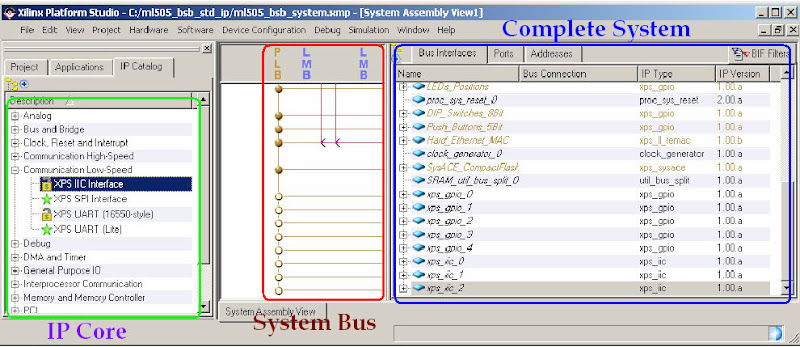

Còn đây là BSB của Xilinx,nhìn chung thì cũng giống của altera thôi nên mình không đi vào chi tiết

* Embedded CPU và IDE

Cũng giống như các ngoại vi,CPU cũng là một IP được viết bằng ngôn ngữ HDL, Altera có NIOS I/NIOS II còn Xilinx có Micro Blaze và pico Blaze. Các hãng khác cũng có các CPU của riêng mình. MicroBlaze và PicoBlaze thì mình không rành nhưng NIOS là CPU 32 bit rất mạnh chạy với tốc độ từ 50->200Mhz có thể đáp ứng được hầu hết các tác vụ xử lý thông thường và ngay cả cài đặt các hệ điều hành nhúng như MicroC/OS-II, uC linux. Altera NIOS II CPU :

+ Kiến trúc RISC (Reduced Instruction Set Computer )

+ Kiến trúc Harvard với bus instruction và data riêng biệt.

+ Maximum pipeline 6 tầng

+ Built-in debugger

+ 32 thanh ghi đa dụng 32-bit

+ Support Cache Controller

+ 32 nguồn ngắt ngoài

+ support cả MMU nếu cần (tức là bộ quản lý bộ nhớ cho mấy hệ điều hành xài)

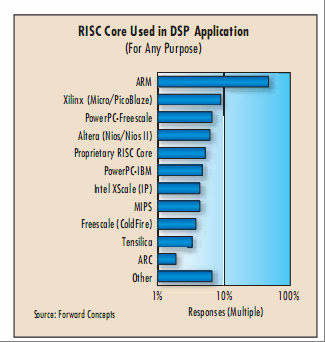

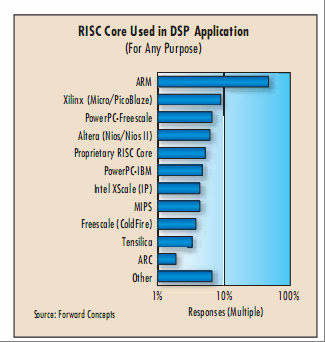

Để tăng cường sức mạnh xử lý cho CPU bên trong FPGA, Xilinx có giải pháp nhúng 1 CPU cứng PowerPC của IBM vào FPGA trên cùng một “die” .Việc sử dụng CPU cứng không những cho phép tăng tốc độ CPU, cải thiện hiệu suất, mà còn không tốn 1 cổng logic nào của FPGA, trong khi các CPU như NIOS thực chất cũng là các IP và được tổng hợp từ các cổng logic của FPGA , các CPU như vậy gọi là “soft CPU”. Các soft CPU được dùng phổ biến không kém các CPU cứng trong các lĩnh vực DSP. Bảng sau chỉ ra mức độ phổ biến của các soft- và hard-CPU core trong các ứng dụng DSP

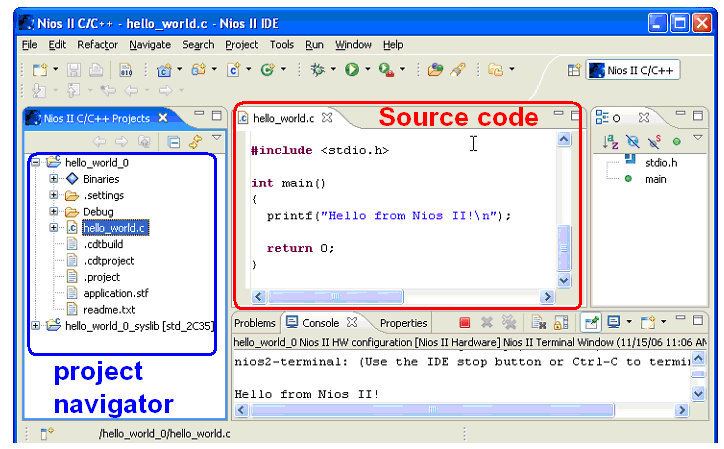

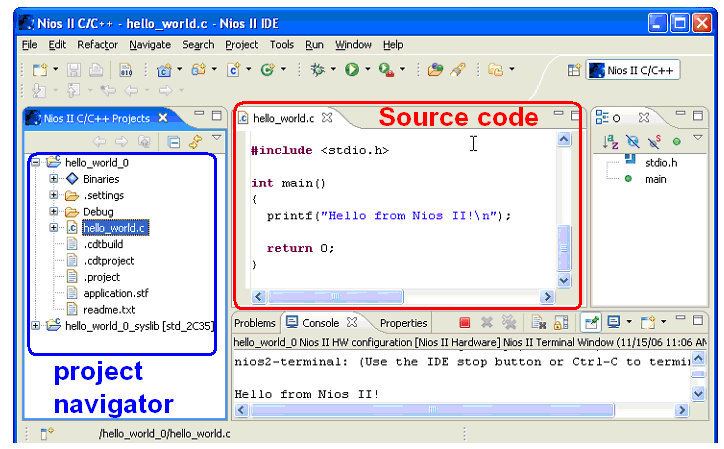

Như vậy chỉ với 1 Chip FPGA. Bạn đã có thể tạo ra một hệ thống tương đương với việc thiết kế một board mạch với CPU, các ngoại vi và các bộ giải mã địa chỉ,…Vần đề còn lại chỉ là làm sao để bạn có thể làm việc với các soft-CPU như giao diện lập trình và programming. Tất nhiên Altera sẽ cung cấp cho bạn một NIOS IDE để bạn lập trình,debug và programming NIOS CPU cũng giống như khi bạn đang làm việc với một Chip MCU/CPU/DSP cứng khác thôi.

Như vậy chỉ với 1 Chip FPGA. Bạn đã có thể tạo ra một hệ thống tương đương với việc thiết kế một board mạch với CPU, các ngoại vi và các bộ giải mã địa chỉ,…Vần đề còn lại chỉ là làm sao để bạn có thể làm việc với các soft-CPU như giao diện lập trình và programming. Tất nhiên Altera sẽ cung cấp cho bạn một NIOS IDE để bạn lập trình,debug và programming NIOS CPU cũng giống như khi bạn đang làm việc với một Chip MCU/CPU/DSP cứng khác thôi.

Dĩ nhiên Xilinx cũng có giải pháp tương tự, nhưng ở đây mình chỉ trình bày NIOS IDE của Altera cho mục đích giới thiệu.

Bài viết có gì thiếu sót mong các bạn góp ý, Hy vọng giúp được các bạn mới bắt đầu Xin chân thành cảm ơn.

Chúc vui,

Saphina

+ Có kiến thức về Hệ thống, kiến trúc máy tính.

+ Biết sử dụng Altera Quartus + SoPC Builder hoặc Xilinx ISE + BSB + XPS

Mặc dù với FPGA ,ta phải xây dựng một một thống từ cổng logic/IC số. Nhưng thực tế không đến nỗi bi đát như vậy. Các nhà sản xuất FPGA cung cấp cho chúng ta các công cụ xây dựng hệ thống cực nhanh (Altera có SoPC Builder, Xilinx có BSB). Thực chất là người ta xây dựng sẵn các thư viện module (khối làm chức năng nào đó) gọi là IP (Intellectual Property) , là sở hữu trí tuệ của những người đã làm ra nó.Vì hệ thống thường có những khối giống nhau, hơn nữa đôi khi chúng ta chỉ muốn phát triển một chức năng nào đó (vd một chip điều khiển PID chằng hạn), trong khi không muốn tốn thời gian thiết kế tòan bộ hệ thống, mà Chip thiết kế ra thì cần phải được đặt trong một hệ thống để có thể hoạt động được. Tuy nhiên nếu bạn muốn bao gồm các IP này trong thiết kế (vd thiết kế của bạn cần 1 IP của các công ty nào đó thì bạn phải lưu ý về bản quyền của IP đó). Thông thường các IP được cung cấp cho chúng ta dùng thử ở dạng mã hóa (bạn không thể nhìn thấy kiến trúc của nó), bạn có thể tạm thời sử dụng chúng cho thiết kế của mình mà không quan tâm đến nội dung bên trong.

Các FPGA vendor hoặc các công ty thứ 3 đều có hầu như đầy đủ tất cả các IP cần thiết cho bạn phát triển hệ thống vd như CPU Core, Timer, UART, JTAG, Memory, DMA controller, Ethernet, USB, SPI, I2C …Sau đây là một ví dụ về một hệ thống hoàn chỉnh

Vấn đề là ta cần một hệ thống BUS để kết nối tất cả nhưng module này lại để hệ thống có thể hoạt động tốt, điều này tưởng chừng như là một vấn đề đơn giản của hệ thống, nhưng thực ra hệ thống bus rất quan trọng và gây ra nhiều vấn đề cho toàn bộ hệ thống vd như chia sẻ băng thông, tốc độ hệ thống …Đôi khi chính hệ thống bus quyết định cả hiệu quả của toàn hệ thống. Nhưng dù sao đi nữa Altera và Xilinx cũng đã giúp ta phần lớn công việc xây dựng system bus bằng các công cụ chuyên dụng. Ở đây mình giới thiệu tổng quan cả hai công cụ của xilinx và altera :

* Altera SoPC Builder (System On Programmable Chip)

Giao diện tạo hệ thống của Altera (SOPC Builder)

Chọn CPU vào hệ thống (Mình bỏ qua việc chọn các thông số cho đơn giản nha)

Thêm Bộ nhớ Cho CPU hoạt động nè (CPU phải có bộ nhớ onChip để chứa Instruction và Data)

Thêm PIO (Parallel Input/Output) cho hệ thống (tức là các Port I/O đa năng ấy mà)

Thêm LED,UART cho thành hệ thống hoàn chỉnh. Chú ý là bạn phải chọn các kết nối cho system connect bus, nếu không CPU sẽ không thể giao tiếp được với các ngoại vi

Bây giờ nhấn nút cái là thành một cái hệ thống hoàn chỉnh, tất cả chỉ mất vài phút cho các hệ thống không quá phức tạp

* Xilinx BSB (Base System Builder) và XPS (Xilinx Platform Studio)

Còn đây là BSB của Xilinx,nhìn chung thì cũng giống của altera thôi nên mình không đi vào chi tiết

* Embedded CPU và IDE

Cũng giống như các ngoại vi,CPU cũng là một IP được viết bằng ngôn ngữ HDL, Altera có NIOS I/NIOS II còn Xilinx có Micro Blaze và pico Blaze. Các hãng khác cũng có các CPU của riêng mình. MicroBlaze và PicoBlaze thì mình không rành nhưng NIOS là CPU 32 bit rất mạnh chạy với tốc độ từ 50->200Mhz có thể đáp ứng được hầu hết các tác vụ xử lý thông thường và ngay cả cài đặt các hệ điều hành nhúng như MicroC/OS-II, uC linux. Altera NIOS II CPU :

+ Kiến trúc RISC (Reduced Instruction Set Computer )

+ Kiến trúc Harvard với bus instruction và data riêng biệt.

+ Maximum pipeline 6 tầng

+ Built-in debugger

+ 32 thanh ghi đa dụng 32-bit

+ Support Cache Controller

+ 32 nguồn ngắt ngoài

+ support cả MMU nếu cần (tức là bộ quản lý bộ nhớ cho mấy hệ điều hành xài)

Để tăng cường sức mạnh xử lý cho CPU bên trong FPGA, Xilinx có giải pháp nhúng 1 CPU cứng PowerPC của IBM vào FPGA trên cùng một “die” .Việc sử dụng CPU cứng không những cho phép tăng tốc độ CPU, cải thiện hiệu suất, mà còn không tốn 1 cổng logic nào của FPGA, trong khi các CPU như NIOS thực chất cũng là các IP và được tổng hợp từ các cổng logic của FPGA , các CPU như vậy gọi là “soft CPU”. Các soft CPU được dùng phổ biến không kém các CPU cứng trong các lĩnh vực DSP. Bảng sau chỉ ra mức độ phổ biến của các soft- và hard-CPU core trong các ứng dụng DSP

Dĩ nhiên Xilinx cũng có giải pháp tương tự, nhưng ở đây mình chỉ trình bày NIOS IDE của Altera cho mục đích giới thiệu.

Bài viết có gì thiếu sót mong các bạn góp ý, Hy vọng giúp được các bạn mới bắt đầu Xin chân thành cảm ơn.

Chúc vui,

Saphina

Comment