Chào bạn Ngoclinh_xl,

Thật sự thì chính tớ mới phải ngưỡng mộ các bạn thì đúng hơn. Lúc tớ học năm thứ 3 thì đến mấy công cụ của cadence, synopsys tớ còn chưa được nghe nói đến chứ nói gì đến việc thiết kế. Thật sự là bây giờ các bạn đã có điều kiện tiếp xúc với những công nghệ hiện đại hơn tớ ngày xưa rất nhiều. Nếu có điều kiện các bạn cố gắng đi "tây du" để phát triển thêm (tớ bắt chước cụ Phan kêu gọi thanh niên )

)

Tớ được may mắn học dưới mái trường xã hội chủ nghĩa và cũng không may mắn ăn phải bả tư bản nên tớ biết so sánh và thấy ăn phải bả tư bản thì sướng hơn . Các bạn cứ từ từ rồi kiểm chứng.

. Các bạn cứ từ từ rồi kiểm chứng.

Thật sự thì chính tớ mới phải ngưỡng mộ các bạn thì đúng hơn. Lúc tớ học năm thứ 3 thì đến mấy công cụ của cadence, synopsys tớ còn chưa được nghe nói đến chứ nói gì đến việc thiết kế. Thật sự là bây giờ các bạn đã có điều kiện tiếp xúc với những công nghệ hiện đại hơn tớ ngày xưa rất nhiều. Nếu có điều kiện các bạn cố gắng đi "tây du" để phát triển thêm (tớ bắt chước cụ Phan kêu gọi thanh niên

)

)Tớ được may mắn học dưới mái trường xã hội chủ nghĩa và cũng không may mắn ăn phải bả tư bản nên tớ biết so sánh và thấy ăn phải bả tư bản thì sướng hơn

. Các bạn cứ từ từ rồi kiểm chứng.

. Các bạn cứ từ từ rồi kiểm chứng.

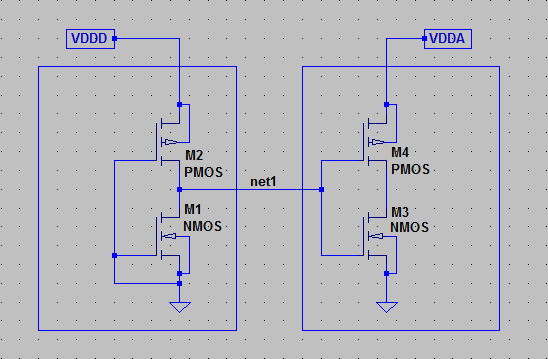

. Theo em nghĩ thì cách khắc phục vấn đề floating point khi giao tiếp giữa một power-managed block với 1 block luôn on là chèn thêm isolation cell như anh Rommel.de đã đề cặp ở trên. Isolation thì có 3 loại:

. Theo em nghĩ thì cách khắc phục vấn đề floating point khi giao tiếp giữa một power-managed block với 1 block luôn on là chèn thêm isolation cell như anh Rommel.de đã đề cặp ở trên. Isolation thì có 3 loại:

Comment