Nguyên văn bởi ngoclinh_xl

Xem bài viết

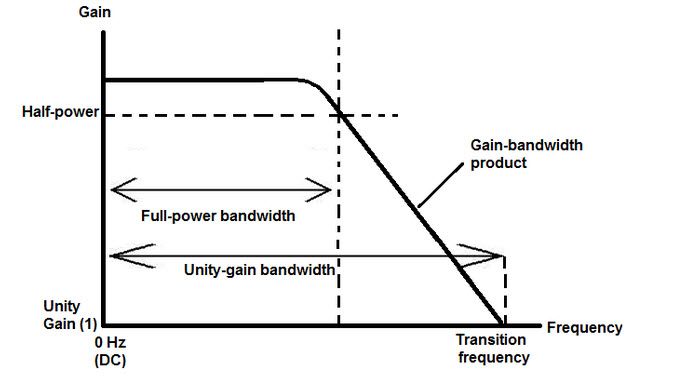

Ở LDO có một trade-off giữa UGB và slew rate dòng, chính cái này là nguyên nhân ảnh hưởng đến spike ở transient response (load step condition). Hai cái thằng này thường gặp trong design LDO, cần phải thiết kế sao cho hai cái thằng này độc lập với nhau, High Slew rate và Large Unity-Gain Bandwidth là điều mà designer mong muốn đạt được. Cái ni chắc Anh Yên rõ hơn bao giờ hết

hihi

hihiVề layout đi metal (lớp trên) qua gate của PowerMos mình nghĩ là không ảnh hưởng, bạn nói là dòng điện chạy trong dây dẫn sinh ra điện trường là chưa đúng đâu nha. Vì điện trường hình thành là do điện áp, bạn cứ layout sao cho các đường đi song song nhau giữa các lớp metal là nhỏ nhất, và nếu như cùng 1 lớp mà có các đường song song thì nên đi giữa nó là GND để shielding. Giữa các metal nên đi vuông góc vừa dễ cho việc debug và tránh ảnh hưởng, VD như bạn quy định M1 đi ngang, M2 đi dọc, M3 đi ngang, M4 đi dọc .... như thế là Ok.

Đó là mấy suy nghĩ của mình, hy vọng giúp đựoc bạn.

Bác thuclh có làm ở sài gòn không vậy ? Em sắp làm ra sản phẩm nên hỏi mọi người kỹ càng cho yên tâm ấy mà. thực ra thì em sắp xong cho nó rồi. Vừa vẽ layout xong nhưng mà lại xóa hết rồi vẽ lại vì lo cái vụ latch-up.

Bác thuclh có làm ở sài gòn không vậy ? Em sắp làm ra sản phẩm nên hỏi mọi người kỹ càng cho yên tâm ấy mà. thực ra thì em sắp xong cho nó rồi. Vừa vẽ layout xong nhưng mà lại xóa hết rồi vẽ lại vì lo cái vụ latch-up.

Comment