Metrology I

Tiện bác hỏi về độ dầy thì tới nói luôn về khâu Metrology. Khâu này là về đo đạc trên wafer.

Trong hãng tớ thì đây không phải là 1 khâu riêng. Mỗi khâu như thinfilm, diffusion đều có phần metrology hết. Nhóm nào thì lo phần metrology của nhóm đó.

Trong khâu thinfilm thì làm sao đo độ dầy của SiO2 được ? Chắc các bác có nhiều lần trong đời nhìn thấy mấy vũng nước mưa mà bị xăng hay dầu từ xe máy nhỏ xuống rồi. Các bác có để ý thấy vết dầu loang này có đủ thứ mầu trên đó không ? Cái này trong quang học kêu là diffraction.

Tớ không rành về quang học lắm nên nói sai thì các bác chỉnh giùm nhé.

Khi ánh sáng chiếu lên mặt lớp dầu loang thì bị phản chiếu lại. Một phần ánh sáng đi qua lớp dầu này và bị phản chiếu bởi mặt nước phía dưới lớp dầu. Vì khúc xạ ánh sáng của dầu nên bước sóng sẽ thay đổi. Khi hai ánh sáng này bị phản chiếu lại thì không còn là ánh sáng trắng nữa mà sẽ bị phân ra thành nhiều mầu khác nhau. Tùy theo độ dầy của lớp dầu loang mà mầu sẽ khác nhau.

Phần metrology đo SiO2 dùng hiện tượng này để đo độ dầy. Một tia sáng chiếu xéo xuống mặt wafer. Mặt SiO2 sẽ phản chiếu 1 phần, phần còn lại thì mặt wafer (phía dưới lớp SiO2) phản chiếu lên. Tùy theo độ dầy của mặt (và cũng tùy theo góc chiếu) mà nó sẽ cho ra những mầu khác nhau.

Link dưới có đưa ra công thức tính độ dầy trong quang học nếu các bác muốn rõ thêm.

http://physics.bu.edu/~duffy/py106/Diffraction.html

Coi phần - a film of oil on water...

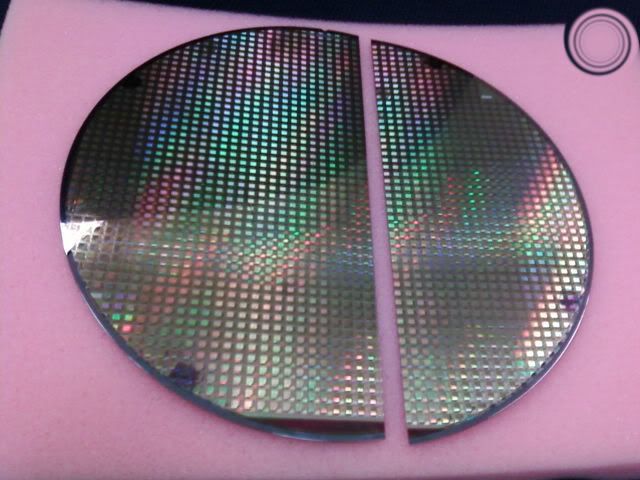

Hình trên cho thấy cùng 1 wafer mà vì ánh sáng đến khác góc mà cho ra những mầu khác nhau.

Máy móc của phần này thì rất phức tạp, nhưng nguyên lý thì rất đơn giản như vết dầu trên vũng nước mưa thôi !

Nguyên văn bởi hithere123

Xem bài viết

Trong hãng tớ thì đây không phải là 1 khâu riêng. Mỗi khâu như thinfilm, diffusion đều có phần metrology hết. Nhóm nào thì lo phần metrology của nhóm đó.

Trong khâu thinfilm thì làm sao đo độ dầy của SiO2 được ? Chắc các bác có nhiều lần trong đời nhìn thấy mấy vũng nước mưa mà bị xăng hay dầu từ xe máy nhỏ xuống rồi. Các bác có để ý thấy vết dầu loang này có đủ thứ mầu trên đó không ? Cái này trong quang học kêu là diffraction.

Tớ không rành về quang học lắm nên nói sai thì các bác chỉnh giùm nhé.

Khi ánh sáng chiếu lên mặt lớp dầu loang thì bị phản chiếu lại. Một phần ánh sáng đi qua lớp dầu này và bị phản chiếu bởi mặt nước phía dưới lớp dầu. Vì khúc xạ ánh sáng của dầu nên bước sóng sẽ thay đổi. Khi hai ánh sáng này bị phản chiếu lại thì không còn là ánh sáng trắng nữa mà sẽ bị phân ra thành nhiều mầu khác nhau. Tùy theo độ dầy của lớp dầu loang mà mầu sẽ khác nhau.

Phần metrology đo SiO2 dùng hiện tượng này để đo độ dầy. Một tia sáng chiếu xéo xuống mặt wafer. Mặt SiO2 sẽ phản chiếu 1 phần, phần còn lại thì mặt wafer (phía dưới lớp SiO2) phản chiếu lên. Tùy theo độ dầy của mặt (và cũng tùy theo góc chiếu) mà nó sẽ cho ra những mầu khác nhau.

Link dưới có đưa ra công thức tính độ dầy trong quang học nếu các bác muốn rõ thêm.

http://physics.bu.edu/~duffy/py106/Diffraction.html

Coi phần - a film of oil on water...

Hình trên cho thấy cùng 1 wafer mà vì ánh sáng đến khác góc mà cho ra những mầu khác nhau.

Máy móc của phần này thì rất phức tạp, nhưng nguyên lý thì rất đơn giản như vết dầu trên vũng nước mưa thôi !

Comment