Mình đang làm Project "Thiết kế Oscilloscope với Kit xtremedsp_devkitIV" muốn cầu kiến các cao thủ vì bế tắc quá.

Ở chế độ đồng bộ ngoài Oscilloscope thường nối 1 đống thiết bị nối tiếp về tín hiệu đồng bộ, vì dụ máy phát hàm, tín hiệu này chuẩn 10Mhz.

Vấn đề đau đầu với mình là cái Kit đang ADC ở 100Mhz chẳng hạn phải chuyển sang chế độ đồng bộ như thế nào, mình có 2 ý tưởng:

1.

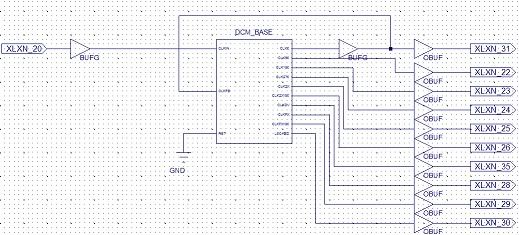

- Đưa xung đồng bộ 10Mhz vào DCM ( IP Core của Xilinx) nâng lên thành 100Mhz.

- Ngắt ngồn xung Clk 100Mhz đang dùng để ADC chuyển sang dùng Clk 100Mhz mới.

Vấn đề là DCM lại không hỗ trợ đầu vào 10Mhz, tối thiểu là 24Mhz mới đau đầu các bác ạ. Bác nào có cách nào để DCM hỗ trợ đầu vào 10Mhz cho ý kiến với?

2.

Lấy Clk đồng bộ 10Mhz vào để điều chỉnh pha của Clk 100Mhz đang ADC.

Bác nào có cao kiến về so pha của hai Clk cho em xin ý kiến với.

Mong tin các cao thủ từng ngày!

Ở chế độ đồng bộ ngoài Oscilloscope thường nối 1 đống thiết bị nối tiếp về tín hiệu đồng bộ, vì dụ máy phát hàm, tín hiệu này chuẩn 10Mhz.

Vấn đề đau đầu với mình là cái Kit đang ADC ở 100Mhz chẳng hạn phải chuyển sang chế độ đồng bộ như thế nào, mình có 2 ý tưởng:

1.

- Đưa xung đồng bộ 10Mhz vào DCM ( IP Core của Xilinx) nâng lên thành 100Mhz.

- Ngắt ngồn xung Clk 100Mhz đang dùng để ADC chuyển sang dùng Clk 100Mhz mới.

Vấn đề là DCM lại không hỗ trợ đầu vào 10Mhz, tối thiểu là 24Mhz mới đau đầu các bác ạ. Bác nào có cách nào để DCM hỗ trợ đầu vào 10Mhz cho ý kiến với?

2.

Lấy Clk đồng bộ 10Mhz vào để điều chỉnh pha của Clk 100Mhz đang ADC.

Bác nào có cao kiến về so pha của hai Clk cho em xin ý kiến với.

Mong tin các cao thủ từng ngày!

[/IMG]

[/IMG]

. 500Mhz mạch ko chạy nổi đâu. Nhân lên chừng 250Mhz là được.

. 500Mhz mạch ko chạy nổi đâu. Nhân lên chừng 250Mhz là được.

Comment