Mình đang thực hành làm quen với FPGA,mình có dùng kit spartan3E(xc3s500) nhưng thấy mấy examp của nó khó quá,mỗi hiển thị lên LCD thối mà mã dài dằng dặc.Có ai đã từng thực tập trên kít này rồi cho mình xin ít ví dụ,project càng tốt,mình cảm ơn!

Thông báo

Collapse

No announcement yet.

LCD kit spartan3E

Collapse

X

-

Cai ISE 6.2i

Mình co cai ISE 6.2 phien ban download cua xilinx nhung khong hieu sao no cu bao loi nhu the nay(hinh duoi day),moi nguoi chi dum voi!

Minh cung cai ban 8.2i nhung nhieu cho thao tac thay khong giong voi chi dan trong guide voi lai nhieu example ho viet bang 6.2 nen khong doc duoc!Technical Institutes

Mobile: 0983278725

Email:

Comment

-

Van de la:minh co dơnload duoc may vi du ve kit spartan3e cua xilinx nhung ho viet toan bang 6.2 nen cac project khong the dung ban 8.2 doc duoc,ma mình lay file nguon .vhd add vao 8.2 thi khi dich bao loi khong tao thanh file .bit duoc,minh muon thu xem ban 6.2 doc va dich nhu the nao hon nua cac tai lieu ho toan huong dan ban 6.2 thoi.Co ban 8.2 ma khong su dung duoc dau qua!Mong moi nguoi chi dan dum,hien minh dang kho khan o cho hien thi LCD.Sao thay ma o cac vi du tren mang dai dang dac vay,vi du nhu doan duoi day?

moi nguoi co the giai thich dum minh doan ma tren khong?Code:////////////////////////////////////// library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity LCD is port( LCD_RS:out std_logic; LCD_RW:out std_logic; LCD_E:out std_logic; clk:in std_logic; SF_D:out std_logic_vector(3 downto 0) ); end LCD; architecture Behavioral of LCD is signal substate,clock,clk1: integer:=0; signal state: integer:=0; begin process(clk) begin clk1<=clk1+1; if(clk1=0) then clock<=clock+1; --WAIT FOR 750000 CLOCK if(state=0 and clock=750000) then state<=1; clock<=0; --WRITE SF_D=0X3 FOR INIATION elsif(state=1) then if(substate=0 and clock=0) then LCD_RS<='1'; LCD_RW<='0'; SF_D<="0000"; Clock<=0; substate<=1; elsif(substate=1 and clock=2) then LCD_E<='1'; Clock<=0; substate<=2; elsif(substate=2 and clock=12) then LCD_E<='0'; substate<=3; Clock<=0; elsif(substate=3 and clock=48) then SF_D<="0011"; Clock<=0; substate<=4; elsif(substate=4 and clock=2) then LCD_E<='1'; Clock<=0; substate<=5; elsif(substate=5 and clock=12) then LCD_E<='0'; substate<=0; state<=2; Clock<=0; end if; --WAIT FOR 2050000 CLOCK elsif(state=2 and clock=205000) then state<=3; clock<=0; --WRITE SF_D=0X3 FOR INIATION elsif(state=3) then if(substate=0 and clock=0) then LCD_RS<='1'; LCD_RW<='0'; SF_D<="0000"; Clock<=0; substate<=1; elsif(substate=1 and clock=2) then LCD_E<='1'; Clock<=0; substate<=2; elsif(substate=2 and clock=12) then LCD_E<='0'; substate<=3; Clock<=0; elsif(substate=3 and clock=48) then SF_D<="0011"; Clock<=0; substate<=4; elsif(substate=4 and clock=2) then LCD_E<='1'; Clock<=0; substate<=5; elsif(substate=5 and clock=12) then LCD_E<='0'; substate<=0; state<=4; Clock<=0; end if; --WAIT 5000 CLOCK elsif(state=4 and clock=5000) then state<=5; clock<=0; --WRITE 0X3 FOR INITIATION elsif(state=5) then if(substate=0 and clock=0) then LCD_RS<='1'; LCD_RW<='0'; SF_D<="0000"; Clock<=0; substate<=1; elsif(substate=1 and clock=2) then LCD_E<='1'; Clock<=0; substate<=2; elsif(substate=2 and clock=12) then LCD_E<='0'; substate<=3; Clock<=0; elsif(substate=3 and clock=48) then SF_D<="0011"; Clock<=0; substate<=4; elsif(substate=4 and clock=2) then LCD_E<='1'; Clock<=0; substate<=5; elsif(substate=5 and clock=12) then LCD_E<='0'; substate<=0; state<=6; Clock<=0; end if; --WAIT 2000 CLOCK elsif(state=6 and clock=2000) then state<=7; clock<=0; --WRITE SF_D=0X2 FOR INITIATION elsif(state=7) then if(substate=0 and clock=0) then LCD_RS<='1'; LCD_RW<='0'; SF_D<="0000"; Clock<=0; substate<=1; elsif(substate=1 and clock=2) then LCD_E<='1'; Clock<=0; substate<=2; elsif(substate=2 and clock=12) then LCD_E<='0'; substate<=3; Clock<=0; elsif(substate=3 and clock=48) then SF_D<="0010"; Clock<=0; substate<=4; elsif(substate=4 and clock=2) then LCD_E<='1'; Clock<=0; substate<=5; elsif(substate=5 and clock=12) then LCD_E<='0'; substate<=0; state<=8; Clock<=0; end if; --WAIT 2000 CLOCK elsif(state=8 and clock=2000) then state<=9; clock<=0; --WRITE FUNCTION SET SD_F = 0X28 elsif(state=9) then if(substate=0 and clock=0) then LCD_RS<='1'; LCD_RW<='0'; SF_D<="0010"; Clock<=0; substate<=1; elsif(substate=1 and clock=2) then LCD_E<='1'; Clock<=0; substate<=2; elsif(substate=2 and clock=12) then LCD_E<='0'; substate<=3; Clock<=0; elsif(substate=3 and clock=48) then SF_D<="1000"; Clock<=0; substate<=4; elsif(substate=4 and clock=2) then LCD_E<='1'; Clock<=0; substate<=5; elsif(substate=5 and clock=12) then LCD_E<='0'; substate<=0; state<=10; Clock<=0; end if; --WAIT 2000 CLOCK elsif(state=10 and clock=2000) then state<=11; clock<=0; --WRITE ENTRY SET SF_D = 0X06 elsif(state=11) then if(substate=0 and clock=0) then LCD_RS<='0'; LCD_RW<='0'; SF_D<="0000"; Clock<=0; substate<=1; elsif(substate=1 and clock=2) then LCD_E<='1'; Clock<=0; substate<=2; elsif(substate=2 and clock=12) then LCD_E<='0'; substate<=3; Clock<=0; elsif(substate=3 and clock=48) then SF_D<="0110"; Clock<=0; substate<=4; elsif(substate=4 and clock=2) then LCD_E<='1'; Clock<=0; substate<=5; elsif(substate=5 and clock=12) then LCD_E<='0'; substate<=0; state<=12; Clock<=0; end if; --WAIT 2000 CLOCK elsif(state=12 and clock=2000) then state<=13; clock<=0; --WRITE DISPLAY ON /OFF SD_F=0X0C elsif(state=13) then if(substate=0 and clock=0) then LCD_RS<='0'; LCD_RW<='0'; SF_D<="0000"; Clock<=0; substate<=1; elsif(substate=1 and clock=2) then LCD_E<='1'; Clock<=0; substate<=2; elsif(substate=2 and clock=12) then LCD_E<='0'; substate<=3; Clock<=0; elsif(substate=3 and clock=48) then SF_D<="1011"; Clock<=0; substate<=4; elsif(substate=4 and clock=2) then LCD_E<='1'; Clock<=0; substate<=5; elsif(substate=5 and clock=12) then LCD_E<='0'; substate<=0; state<=14; Clock<=0; end if; --WAIT 2000 CLOCK elsif(state=14 and clock=2000) then state<=15; clock<=0; --WRITE CLEAR DISPLAY COMMAND SF_D<=0x HAVE TO FIX THIS elsif(state=15) then if(substate=0 and clock=0) then LCD_RS<='0'; LCD_RW<='0'; SF_D<="0000";-- I HAVE FIXED IT Clock<=0; substate<=1; elsif(substate=1 and clock=2) then LCD_E<='1'; Clock<=0; substate<=2; elsif(substate=2 and clock=12) then LCD_E<='0'; substate<=3; Clock<=0; elsif(substate=3 and clock=48) then SF_D<="0001";-- I HAVE FIXED IT Clock<=0; substate<=4; elsif(substate=4 and clock=2) then LCD_E<='1'; Clock<=0; substate<=5; elsif(substate=5 and clock=12) then LCD_E<='0'; substate<=0; state<=16; Clock<=0; end if; --WAIT FOR 82,000 CLOCK elsif(state=16 and clock=82000) then state<=17; clock<=0; --WRITE SET DD RAM ADD SF_D<=0x HAVE TO FIX THIS elsif(state=17) then if(substate=0 and clock=0) then LCD_RS<='0'; LCD_RW<='0'; SF_D<="1000";--IT HAS BEEN FIXED Clock<=0; substate<=1; elsif(substate=1 and clock=2) then LCD_E<='1'; Clock<=0; substate<=2; elsif(substate=2 and clock=12) then LCD_E<='0'; substate<=3; Clock<=0; elsif(substate=3 and clock=48) then SF_D<="0000";-- IT HAS BEEN FIXED Clock<=0; substate<=4; elsif(substate=4 and clock=2) then LCD_E<='1'; Clock<=0; substate<=5; elsif(substate=5 and clock=12) then LCD_E<='0'; substate<=0; state<=18; Clock<=0; end if; --WAIT FOR 2,000 CLOCK elsif(state=18 and clock=2000) then state<=19; clock<=0; --WRITE DD RAM ADD SF_D<=0x HAVE TO FIX THIS elsif(state=19) then if(substate=0 and clock=0) then LCD_RS<='1'; LCD_RW<='0'; SF_D<="0100";--IT HAS BEEN FIXED Clock<=0; substate<=1; elsif(substate=1 and clock=2) then LCD_E<='1'; Clock<=0; substate<=2; elsif(substate=2 and clock=12) then LCD_E<='0'; substate<=3; Clock<=0; elsif(substate=3 and clock=48) then SF_D<="0001";-- IT HAS BEEN FIXED Clock<=0; substate<=4; elsif(substate=4 and clock=2) then LCD_E<='1'; Clock<=0; substate<=5; elsif(substate=5 and clock=12) then LCD_E<='0'; substate<=0; state<=20; Clock<=0; end if; elsif(state=20)then state<=20; clock<=0; end if; elsif(clk1=1) then clk1<=0; end if; end process; end Behavioral; /////////////////////////////////////////Last edited by namqn; 17-09-2007, 19:18.Technical Institutes

Mobile: 0983278725

Email:

Comment

-

Các file HDL đều tuân theo chuẩn IEEE. Bạn không thấy ở đầu họ dùng thư viện IEEE sao.

Còn về code dài thì tất nhiên rùi. Vì bạn đọc datasheet của LCD, giao thức để giao tiếp với LCD phức tạp chứ có phải đưa dữ liệu ra là nó tự hiển thị cho bạn đâu.Code:library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL;

Bạn đọc kĩ từng bước một sẽ hiểu ngay mà. Code của bạn nên để trong tag code cho dễ đọc nhé.

Thứ 2 là HDL là ngôn ngữ miêu tả phần cứng do đó một project tạo bởi ISE 6.2 phải đọc được ở bản 8.2 chứ. Nếu không được bạn tạo một project và add source các component đó vào.

Chú bạn thành công.Technical sale at WT Microelectronics S'pore

Hỗ trợ dự án sử dụng các hãng Texas Instrument, STMicro, Freescale, Fairchild, International Rectifier, Ublox, Lumiled, Maxim

Liên hệ: 0915.560.511 hoặc ngo.haibac@wtmec.com

Comment

-

Tui setup project chạy trên ISE 8.2 rồi, không có vấn đề gì cả, bác xem lại thử xem. Các bước thực hiện như sau:

New Project -> Chọn Device -> add VHDL source -> Synthesize -> Constraint, asign pins -> generate programming file.

Cái này làm chơi chơi để hiểu thêm thôi, nên dùng phần điểu khiển firmware để có thể thay đổi hiển thị theo mong muốn.

Comment

-

LCD demo cho microblaze

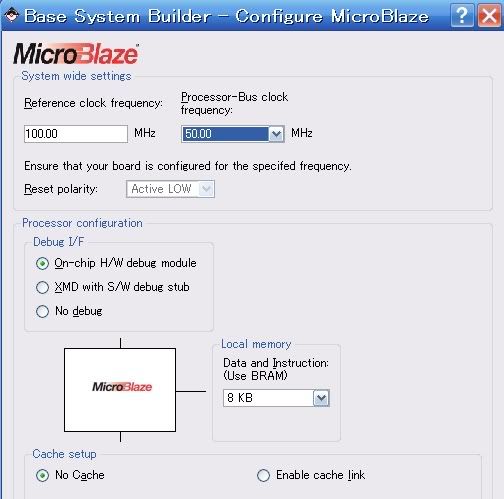

Sau đây là các bước thực hiện LCD demo cho microblaze.

Tool : EDK 8.2

Demo trên board ML403, tuy nhiên vẫn có thể thay đổi chút ít cho board Spartan3E Starter

Hướng dẫn step by step, hình hơi nhiều, chữ thì ít ( lười viết mà) thông cảm nhá.

Chú ý: Vài bước được thông qua ( để mặc định và ấn nút next) thay vì post hình đầy đủ.

----------------------------------------------------------------------

PHAN 1 : Setup hardware

----------------------------------------------------------------------

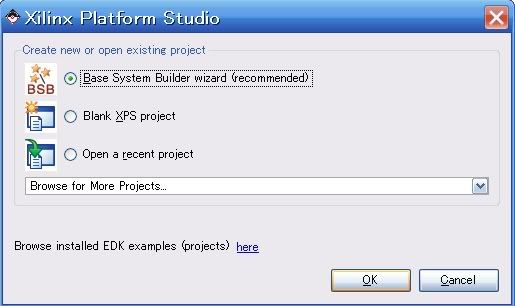

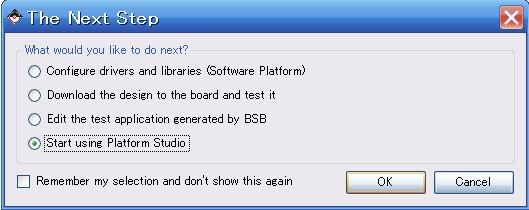

1> Start XPS 8.2i

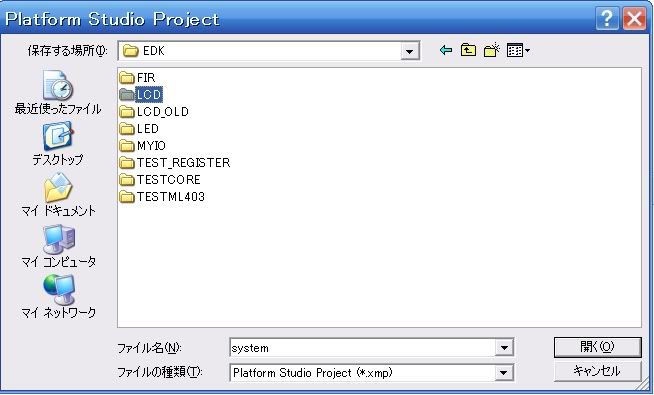

2> Tạo thư mục chứa project

3> Creat new base system

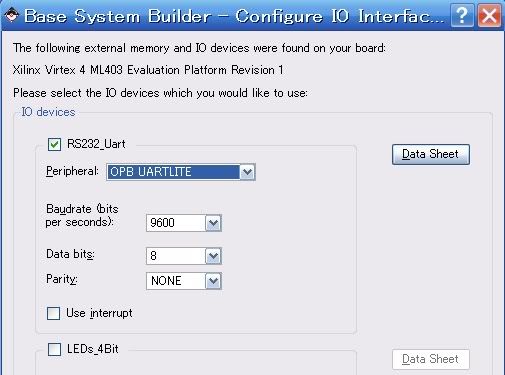

4> Select Board (chú ý: một số board có nhiều revision khác nhau, nên chọn revison thích hợp)

5> Chọn món ăn tùy vào túi tiền

Last edited by kamejoko80; 18-09-2007, 06:04.

Last edited by kamejoko80; 18-09-2007, 06:04.

Comment

-

LCD demo cho microblaze 2

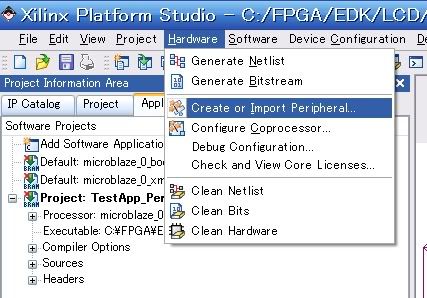

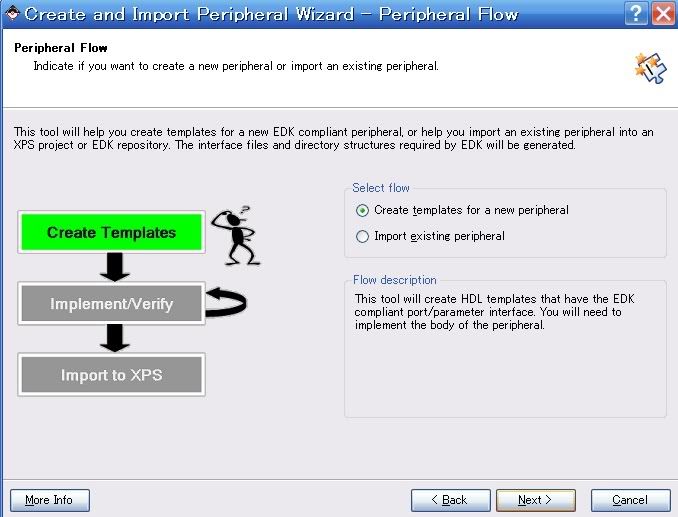

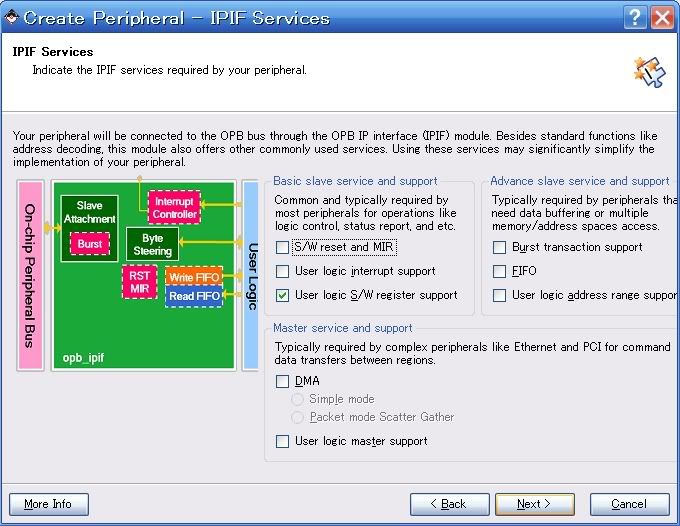

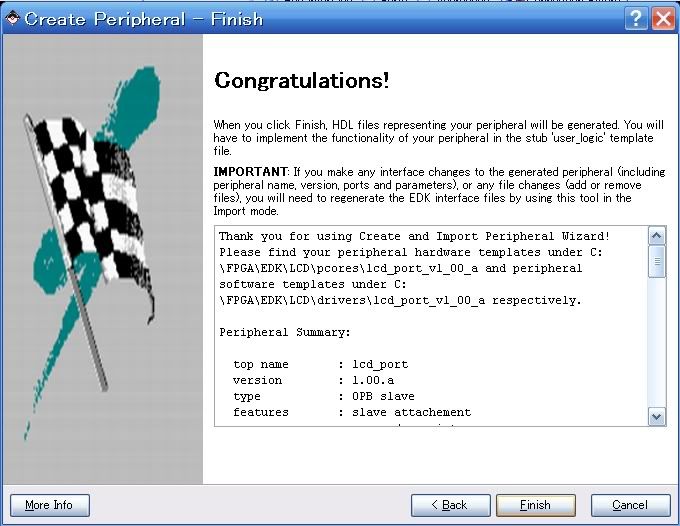

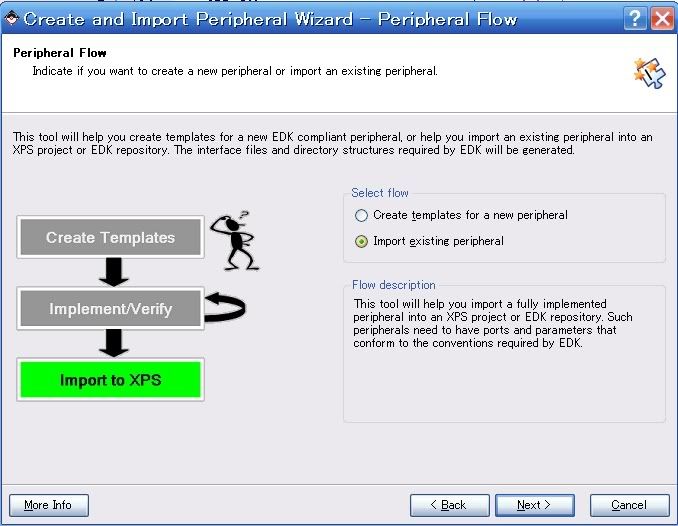

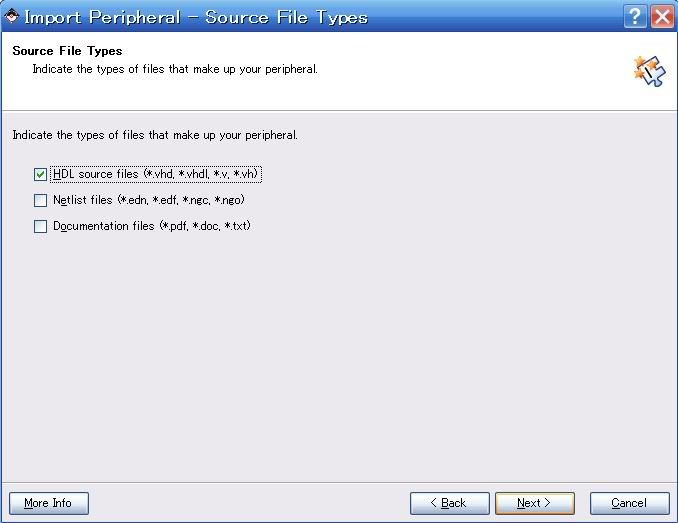

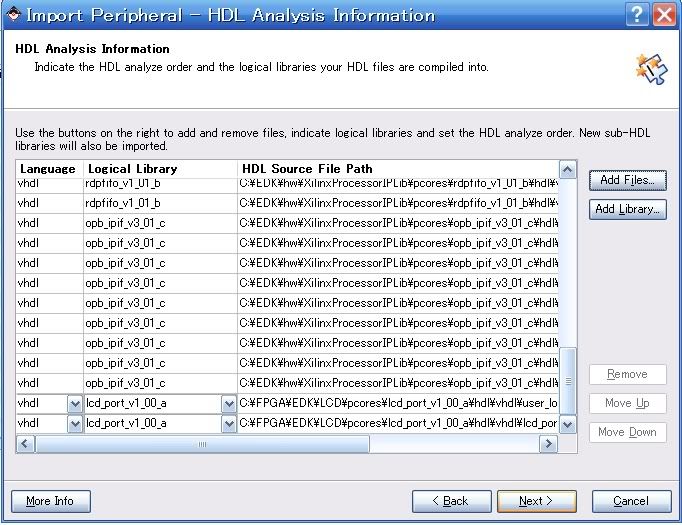

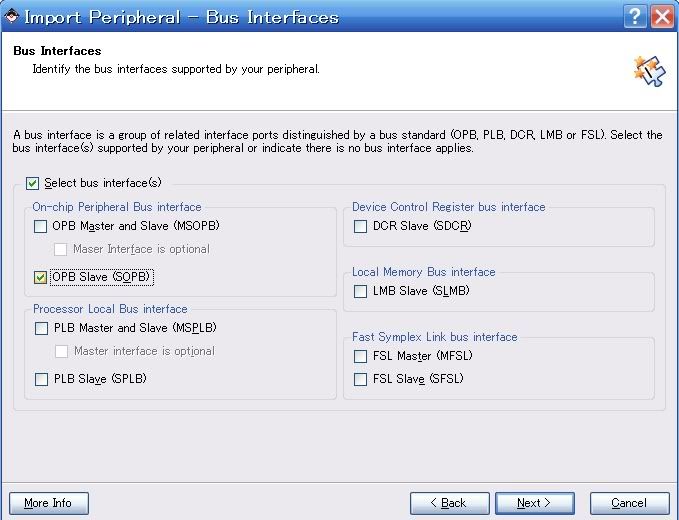

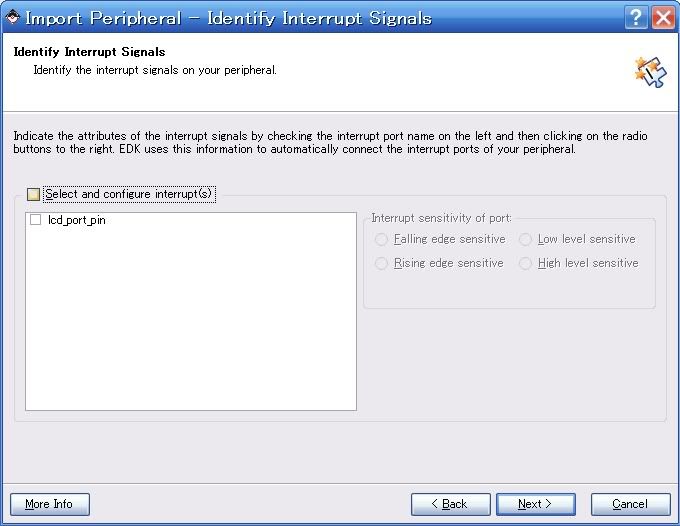

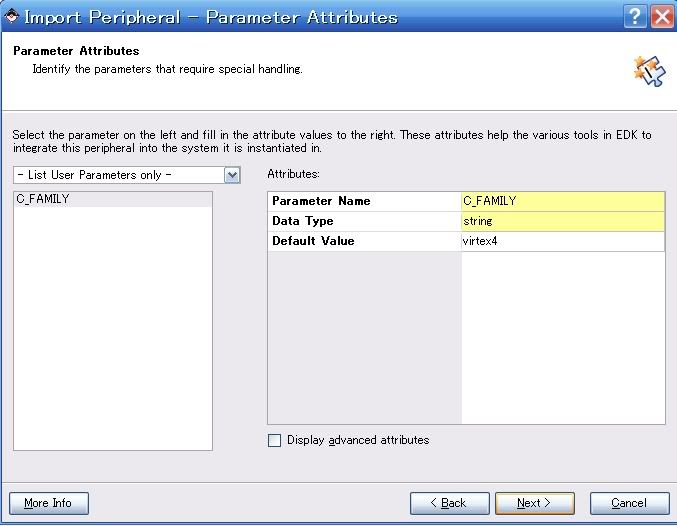

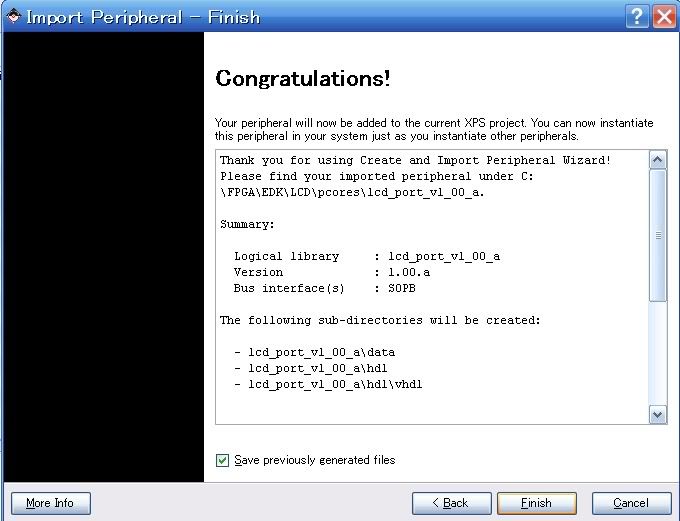

6> Creat Custom hardware (lcd port)

Sau khi hoàn tất các bước trên, XPS tạo ra các file có cấu trúc như sau:

Phần hardware chứa trong thư mục pcores, bao gồm tên (lcd_port) gắn với version hardware chỉ định (lcd_port_v1_00_a)

Phần software chứa trong thư mục drivers (sẽ được trình bày trong phần sau)

Last edited by kamejoko80; 18-09-2007, 06:01.

Last edited by kamejoko80; 18-09-2007, 06:01.

Comment

-

LCD demo cho microblaze 3

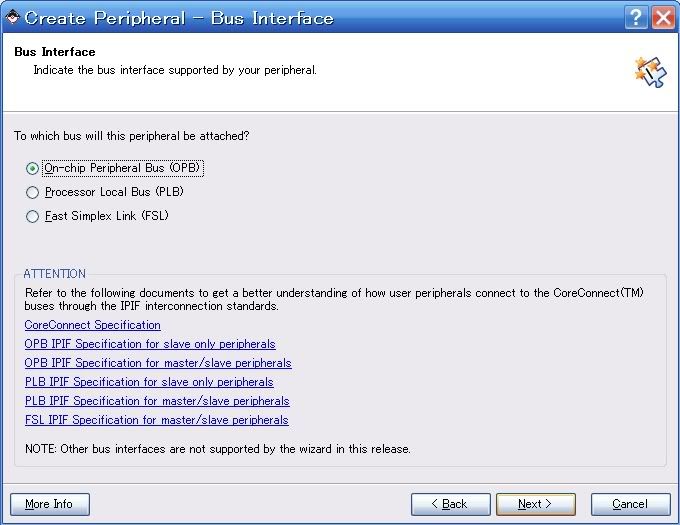

7> Edit custom hardware

Sau khi thực hiện xong thao tác creat custom peipheral (dùng bus OPB), XPS tạo ra 2 file source vhdl bao gồm name.vhd và user_logic.vhd chứa trong thư mục vhdl

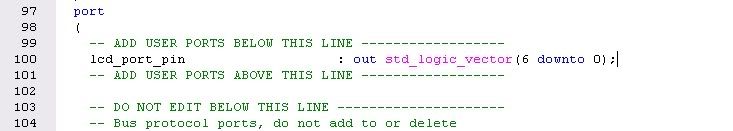

8> Edit user_logic.vhd

goto hàng (khoảng 100) add user port theo hình sau:

XPS tạo thanh ghi "slv_reg0" cho truy xuất với customer ip core, trong trường hợp này ta gán cho port xuất lcd

goto hàng (khoảng 208-209) add code như hình sau

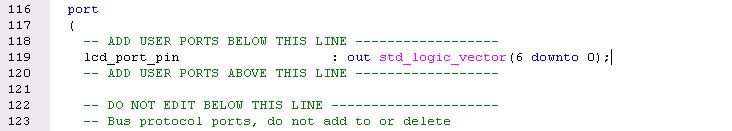

9> Edit lcd_port.vhd

goto hàng (khoảng 119) add user port theo hình sau:

goto hàng (khoảng 388) map port

Xong bước creat , edit customer OPB port

Comment

-

LCD demo cho microblaze 5

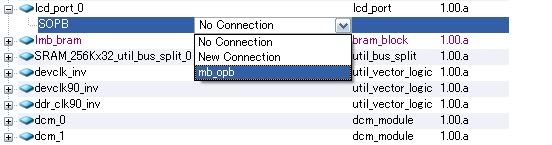

11> Add ipcore vào bus OBP

Trên tab IP Catalog chọn Project Repository, click chuột phải vào lcd_port chọn add IP

Trên mục system assembly view ta thấy custom ip core lcd_port_0 được add vào, lúc này lcd_port_0 chưa thật sự được gắn vào bus OPB, ta thực hiện bước connect vào OPB theo hình sau:

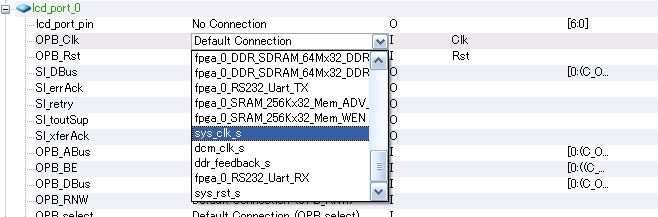

Chọn nút radio của mục port , connection filters chọn all để hiển thị tất cả các đường kết nối.

OPB_clk -> sys_clk_s : system clock source

lcd_port_pin -> Make external

Sau khi kết nối lcd_port_pin với external port, mục trên cùng External Ports xuất hiện đường kết nối lcd_port_0_lcd_port_pin, rename phần tên kết nối phía bên trái để tiện cho việc assign pin constrain.

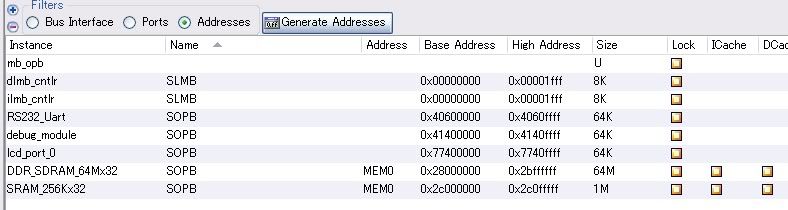

Chọn nút radio address, trong mục size (kích thước vùng nhớ cho ngoại vi) trong drop list chọn 64K, sau đó chọn Generate Addresses, Xillin tự động tính toán các đường địa chỉ và remap lại cho toàn bộ ngoại vi.

Cuối cùng là bước assign constrain pins cho lcd_port, tùy theo kết nối của các board khác nhau ta có các khai báo gán pins khác nhau.

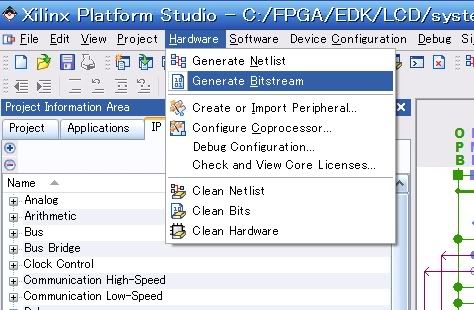

Tool -> Hardware -> Generate Bitstream. Đến bước này ta có thể thong thả ngồi uống Coca chờ đợi XPS hoàn tất cho phần hardware.

Đuối roài !!!, hôm nay tạm ngưng ở đây, hôm sau trình bày tiếp về phần firmware.

Comment

Bài viết mới nhất

Collapse

-

Trả lời cho Công suất truyền qua lõi máy biến ápbởi NGULAUCái chỗ mà vandong1111 bôi đỏ không phải do chủ thớt nghĩ ra, cũng chẳng phải do TLM sáng tác. Mà nó có ghi trong giáo trình máy biến áp: https://www.hnue.edu.vn/Portals/0/Te...he-dien-tu.pdf

Sao trang không vào được bạn-

Channel: Điện tử công suất

hôm nay, 12:06 -

-

bởi vi van phamBởi vậy khi nói kỹ thuật là phải nói chi tiết rõ ràng, chân vịt 3 cánh to tốc độ thấp lưu lượng mạnh nhất còn không chấp nhận, 6 cánh xếp chồng nhau người ta ko gọi là quạt mà gọi đó là máy nén khí. Lấy kinh nghiệm lý giải kỹ thuật thì đến tết mới xong....

-

Channel: Điện tử gia dụng

hôm nay, 11:16 -

-

bởi dinhthuong80Cháu có chút thất vọng! Sao bác không lấy loại cánh 3 lá nhỏ với 5 lá nhỏ chẳng hạn (tỉ số sẽ 5/3, không phải 2/1); hay cánh kim loại 2 lá với 4 lá; Còn nếu bác thích loại 3 lá to kiểu tai voi thông dụng thì nếu cần sản xuất, làm 6 lá...

-

Channel: Điện tử gia dụng

hôm nay, 11:09 -

-

bởi vi van pham1- 6 người chưa chắc mang 6 kg hàng trong 1 phút vì sức khỏe khác nhau.

2- Tương tự 3 cánh quạt to, độ nghiêng và diện tích 3 cánh chiếm hết 360 độ không gian cánh quạt, nếu 6 cánh thì dôi ra 3 cánh sẽ xếp nó vào nơi nào? kiến thức...-

Channel: Điện tử gia dụng

hôm nay, 10:26 -

-

bởi dinhthuong80Đến giờ thì Đình Thường tôi thật sự cảm thấy tiền mình bỏ ra mua quạt và thiết bị đo, thời gian và công sức mình thí nghiệm đo kiểm và đưa lên đây giới thiệu cho mọi người thật là uổng phí!. Nói gì, đưa ra bằng chứng gì cũng...

-

Channel: Điện tử gia dụng

hôm nay, 09:35 -

-

bởi tuyennhanTôi vào trang cafef xem thì không có số liệu gì vào tiếp trang nơi bán ở sin thì có số liệu thì thấy quạt 3 cánh lưu lượng gió kém hơn 5 cánh nhưng cstt nhỏ hơn và là quạt trần dc cánh nhỏ không có quạt bàn cánh to .

Vào trang của hãng...-

Channel: Điện tử gia dụng

hôm nay, 07:35 -

-

bởi vi van phamMẹ từ đồng ruộng về, mồ hôi ướt đẩm mặt mẹ.

Mẹ ko còn sức vẩy cái nón nữa. Mẹ như cái motor hết pin.

Thằng quạt nhỏ cười toe toét quạt lấy , quạt để khoe chân lý quạt nhỏ mát hơn quạt to.

...

...

-

Channel: Điện tử gia dụng

hôm nay, 07:19 -

-

Trả lời cho Hỗ trợ tìm linh kiện mạch hạ áp 220V - 110Vbởi ngtuhanCòn thiếu con trở 330 ohm/10W nối song song CE của transitor công suất. Mạch này có từ cái thời VN dùng tivi nội địa Nhật, thay thế cho phần ổn áp 110v (nếu bị hỏng). Giờ chỉ là dĩ vãng.

-

Channel: Hướng dẫn tìm thông tin linh kiện

hôm nay, 02:27 -

-

bởi dinhthuong80[QUOTE=nhathung1101;n1735558]

Thế theo bác thì thằng rung đùi kia sẽ nói thằng cánh to hay thằng cánh nhỏ quay nhanh hơn? Thằng thuốc rượu nói thằng nhỏ hay thằng to mạnh hơn??...-

Channel: Điện tử gia dụng

hôm nay, 00:50 -

-

bởi nhathung1101Ngày xửa ngày xưa còn dùng quạt 1 cánh, dù vẩy hết tốc độ cho cái mo cau chóng mặt mà chả ăn thua.

Mẹ vẩy nhẹ cái nón mà mát lịm cả người. Thế nên phải hiểu chiều sâu mới được.

Cái nón sâu hơn cái mo cau là...-

Channel: Điện tử gia dụng

Hôm qua, 23:34 -

Comment