Em mới tập tành với FPGA , có một mạch và 2 phần mềm EDK , ISE . Tìm được trên mạng cái file "import_peripheral_tutorial"(cái này chắc nhiều người biết)và làm giống như nó chỉ , có vài điều chưa rõ ràng mong các bro giúp đỡ

Đây là file user_logic.vhd mà em đã làm theo

Em muốn hỏi là sau khi làm xong đưa trở lại EDK để sử dụng thì làm sao để sử dụng port digit_n cũng như những port khác như segment_n hay Bus2IP_reset....vậy .Vì em thấy khi khởi tạo cái này có bước là chọn thanh ghi,thì nó bảo chọn là số lượng :1 và 32bit.

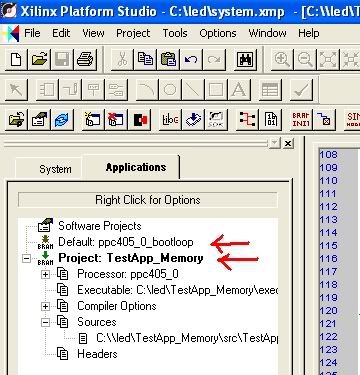

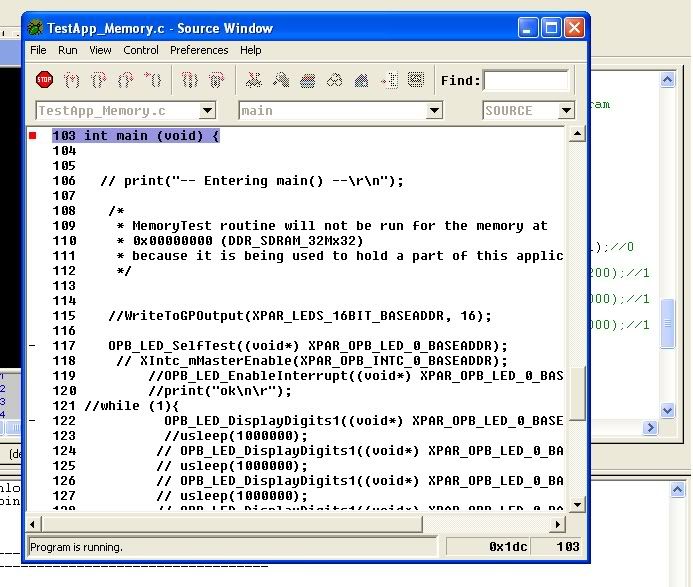

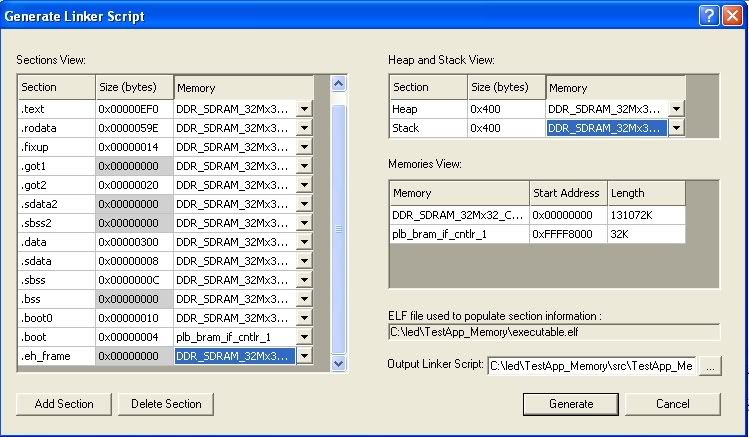

Và trong file system.ucf(EDK) em đã thử gán những port digit_n và segment_n tới những con led trên mạch(mạch em có 16 con led).Sau đó đánh đoạn code C sau vào file TestApp_Memory (sau khi đã làm những bước thêm vài một số code trong các file.h,file.c trong phần driver như hướng dẫn)

-------------------------------------------------------------------

Void OPB_7SEGLED_DISPLAYDIGITS(void *baseaddr_p , Xuint32 data)

{

Xuint32 baseaddr;

baseaddr=(Xuint32) baseaddr_p;

XIo_out8(Baseaddr,data);

}

int main (void) {

OPB_7SEGLED_SelfTest((void*)XPAR_OPB_7SEGLED_0_BAS EADDR);

////cái dòng này chỉ là lệnh khởi tạo thôi phải hông các anh?????

OPB_7SEGLED_DISPLAYDIGITS((void*)XPAR_OPB_7SEGLED_ 0_BASEADDR,3);

////giá trị 3 tương ứng với việc hiển thị số 0 trên led 7 đoạn

return 0;

}

Sau đó chạy thử thì thấy những led mà được gán đến "port segment_n" hiển thị rất đúng(cái này làm thử đại chứ không biết gì) , còn những led được gán tới "port digit_n" thì em không biết phải sử dụng ra sao

-------------------------------------------------------------------

USER_LOGIC.VHL

--------------------------------------

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

library proc_common_v2_00_a;

use proc_common_v2_00_a.proc_common_pkg.all;

entity user_logic is

generic

(

C_DWIDTH : integer := 32;

C_NUM_CE : integer := 1;

C_IP_INTR_NUM : integer := 1

);

port

(

digit_n : out std_logic_vector(0 to 3);

segment_n : out std_logic_vector(0 to 7);

Bus2IP_Clk : in std_logic;

Bus2IP_Reset : in std_logic;

IP2Bus_IntrEvent : out std_logic_vector(0 to C_IP_INTR_NUM-1);

Bus2IP_Data : in std_logic_vector(0 to C_DWIDTH-1);

Bus2IP_BE : in std_logic_vector(0 to C_DWIDTH/8-1);

Bus2IP_RdCE : in std_logic_vector(0 to C_NUM_CE-1);

Bus2IP_WrCE : in std_logic_vector(0 to C_NUM_CE-1);

IP2Bus_Data : out std_logic_vector(0 to C_DWIDTH-1);

IP2Bus_Ack : out std_logic;

IP2Bus_Retry : out std_logic;

IP2Bus_Error : out std_logic;

IP2Bus_ToutSup : out std_logic

);

end entity user_logic;

------------------------------------------------------------------------------

-- Architecture section

------------------------------------------------------------------------------

architecture IMP of user_logic is

type CTRL_REG is array (0 to 3) of std_logic_vector(0 to 7);

signal display_ctrl : CTRL_REG;

signal digit_select : std_logic_vector(0 to 1);

signal digit_n_i : std_logic_vector(0 to 3);

signal segment_n_i : std_logic_vector(0 to 7);

signal mhertz_cnt : std_logic_vector(0 to 5);

signal khertz_cnt : std_logic_vector(0 to 9);

signal hertz_cnt : std_logic_vector(0 to 9);

signal mhertz_en : std_logic;

signal khertz_en : std_logic;

signal hertz_en : std_logic;

signal slv_reg0 : std_logic_vector(0 to C_DWIDTH-1);

signal slv_reg_write_select : std_logic_vector(0 to 0);

signal slv_reg_read_select : std_logic_vector(0 to 0);

signal slv_ip2bus_data : std_logic_vector(0 to C_DWIDTH-1);

signal slv_read_ack : std_logic;

signal slv_write_ack : std_logic;

signal interrupt : std_logic_vector(0 to C_IP_INTR_NUM-1);

begin

display_ctrl(0) <= slv_reg0(0 to 7);

display_ctrl(1) <= slv_reg0(8 to 15);

display_ctrl(2) <= slv_reg0(16 to 23);

display_ctrl(3) <= slv_reg0(24 to 31);

digit_n <= digit_n_i;

segment_n <= segment_n_i;

---------------------------------------

-- Clock Dividers

---------------------------------------

GEN_1MHZ_PROCESS : process( Bus2IP_Clk ) is

begin

if Bus2IP_Clk'event and Bus2IP_Clk = '1' then

if Bus2IP_Reset = '1' then

mhertz_cnt <= (others => '0');

mhertz_en <= '0';

else

mhertz_cnt <= mhertz_cnt + 1;

if mhertz_cnt = "110010" then

mhertz_en <= '1' ;

mhertz_cnt <= (others => '0');

else

mhertz_en <= '0';

end if;

end if;

end if;

end process GEN_1MHZ_PROCESS;

GEN_1KHZ_PROCESS : process( Bus2IP_Clk ) is

begin

if Bus2IP_Clk'event and Bus2IP_Clk = '1' then

if Bus2IP_Reset = '1' then

khertz_cnt <= (others => '0');

khertz_en <= '0';

else

if mhertz_en = '1' then

khertz_cnt <= khertz_cnt + 1;

if khertz_cnt = "1111101000" then

khertz_en <= '1';

khertz_cnt <= (others => '0');

end if;

else

khertz_en <= '0';

end if;

end if;

end if;

end process GEN_1KHZ_PROCESS;

GEN_1HZ_PROCESS : process( Bus2IP_Clk ) is

begin

if Bus2IP_Clk'event and Bus2IP_Clk = '1' then

if Bus2IP_Reset = '1' then

hertz_cnt <= (others => '0');

hertz_en <= '0';

else

if khertz_en = '1' then

hertz_cnt <= hertz_cnt + 1;

if hertz_cnt = "1111101000" then

hertz_en <= '1';

hertz_cnt <= (others => '0');

end if;

else

hertz_en <= '0';

end if;

end if;

end if;

end process GEN_1HZ_PROCESS;

----------------------------------------

-- Display Update

----------------------------------------

CYC_DISP_PROCESS : process( Bus2IP_Clk ) is

begin

if Bus2IP_Clk'event and Bus2IP_Clk = '1' then

if Bus2IP_Reset = '1' then

digit_select <= (others => '0');

digit_n_i <= (others => '1');

segment_n_i <= (others => '1');

else

if khertz_en = '1' then

digit_select <= digit_select + 1;

case digit_select is

When "00" => segment_n_i <= display_ctrl(0);

digit_n_i <= "1110";

When "01" => segment_n_i <= display_ctrl(2);

digit_n_i <= "1101";

When "10" => segment_n_i <= display_ctrl(3);

digit_n_i <= "1011";

When "11" => segment_n_i <= display_ctrl(3);

digit_n_i <= "0111";

When others => null;

end case;

end if;

end if;

end if;

end process CYC_DISP_PROCESS;

slv_reg_write_select <= Bus2IP_WrCE(0 to 0);

slv_reg_read_select <= Bus2IP_RdCE(0 to 0);

slv_write_ack <= Bus2IP_WrCE(0);

slv_read_ack <= Bus2IP_RdCE(0);

-- implement slave model register(s)

SLAVE_REG_WRITE_PROC : process( Bus2IP_Clk ) is

begin

if Bus2IP_Clk'event and Bus2IP_Clk = '1' then

if Bus2IP_Reset = '1' then

slv_reg0 <= (others => '1');

else

case slv_reg_write_select is

when "1" =>

for byte_index in 0 to (C_DWIDTH/8)-1 loop

if ( Bus2IP_BE(byte_index) = '1' ) then

slv_reg0(byte_index*8 to byte_index*8+7) <= Bus2IP_Data(byte_index*8 to byte_index*8+7);

end if;

end loop;

when others => null;

end case;

end if;

end if;

end process SLAVE_REG_WRITE_PROC;

-- implement slave model register read mux

SLAVE_REG_READ_PROC : process( slv_reg_read_select, slv_reg0 ) is

begin

case slv_reg_read_select is

when "1" => slv_ip2bus_data <= slv_reg0;

when others => slv_ip2bus_data <= (others => '0');

end case;

end process SLAVE_REG_READ_PROC;

INTR_PROC : process( Bus2IP_Clk ) is

constant COUNT_SIZE : integer := 30;

constant ALL_ONES : std_logic_vector(0 to COUNT_SIZE-1) := (others => '1');

variable counter : std_logic_vector(0 to COUNT_SIZE-1);

begin

if ( Bus2IP_Clk'event and Bus2IP_Clk = '1' ) then

if ( Bus2IP_Reset = '1' ) then

counter := (others => '0');

interrupt <= (others => '0');

else

counter := counter + 1;

if ( counter = ALL_ONES ) then

interrupt <= (others => '1');

else

interrupt <= (others => '0');

end if;

end if;

end if;

end process INTR_PROC;

IP2Bus_IntrEvent(0) <= hertz_en;

IP2Bus_Data <= slv_ip2bus_data;

IP2Bus_Ack <= slv_write_ack or slv_read_ack;

IP2Bus_Error <= '0';

IP2Bus_Retry <= '0';

IP2Bus_ToutSup <= '0';

end IMP;

--------------------------------------------------------------------

MONG CÁC ANH CHỈ DẪN GIÚPgửi kèm file "import_peripheral_tutorial" và rất mong sự giúp đỡ . CÁM ƠN NHIỀU

http://www.megaupload.com/?d=7HKDLS77

Đây là file user_logic.vhd mà em đã làm theo

Em muốn hỏi là sau khi làm xong đưa trở lại EDK để sử dụng thì làm sao để sử dụng port digit_n cũng như những port khác như segment_n hay Bus2IP_reset....vậy .Vì em thấy khi khởi tạo cái này có bước là chọn thanh ghi,thì nó bảo chọn là số lượng :1 và 32bit.

Và trong file system.ucf(EDK) em đã thử gán những port digit_n và segment_n tới những con led trên mạch(mạch em có 16 con led).Sau đó đánh đoạn code C sau vào file TestApp_Memory (sau khi đã làm những bước thêm vài một số code trong các file.h,file.c trong phần driver như hướng dẫn)

-------------------------------------------------------------------

Void OPB_7SEGLED_DISPLAYDIGITS(void *baseaddr_p , Xuint32 data)

{

Xuint32 baseaddr;

baseaddr=(Xuint32) baseaddr_p;

XIo_out8(Baseaddr,data);

}

int main (void) {

OPB_7SEGLED_SelfTest((void*)XPAR_OPB_7SEGLED_0_BAS EADDR);

////cái dòng này chỉ là lệnh khởi tạo thôi phải hông các anh?????

OPB_7SEGLED_DISPLAYDIGITS((void*)XPAR_OPB_7SEGLED_ 0_BASEADDR,3);

////giá trị 3 tương ứng với việc hiển thị số 0 trên led 7 đoạn

return 0;

}

Sau đó chạy thử thì thấy những led mà được gán đến "port segment_n" hiển thị rất đúng(cái này làm thử đại chứ không biết gì) , còn những led được gán tới "port digit_n" thì em không biết phải sử dụng ra sao

-------------------------------------------------------------------

USER_LOGIC.VHL

--------------------------------------

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

library proc_common_v2_00_a;

use proc_common_v2_00_a.proc_common_pkg.all;

entity user_logic is

generic

(

C_DWIDTH : integer := 32;

C_NUM_CE : integer := 1;

C_IP_INTR_NUM : integer := 1

);

port

(

digit_n : out std_logic_vector(0 to 3);

segment_n : out std_logic_vector(0 to 7);

Bus2IP_Clk : in std_logic;

Bus2IP_Reset : in std_logic;

IP2Bus_IntrEvent : out std_logic_vector(0 to C_IP_INTR_NUM-1);

Bus2IP_Data : in std_logic_vector(0 to C_DWIDTH-1);

Bus2IP_BE : in std_logic_vector(0 to C_DWIDTH/8-1);

Bus2IP_RdCE : in std_logic_vector(0 to C_NUM_CE-1);

Bus2IP_WrCE : in std_logic_vector(0 to C_NUM_CE-1);

IP2Bus_Data : out std_logic_vector(0 to C_DWIDTH-1);

IP2Bus_Ack : out std_logic;

IP2Bus_Retry : out std_logic;

IP2Bus_Error : out std_logic;

IP2Bus_ToutSup : out std_logic

);

end entity user_logic;

------------------------------------------------------------------------------

-- Architecture section

------------------------------------------------------------------------------

architecture IMP of user_logic is

type CTRL_REG is array (0 to 3) of std_logic_vector(0 to 7);

signal display_ctrl : CTRL_REG;

signal digit_select : std_logic_vector(0 to 1);

signal digit_n_i : std_logic_vector(0 to 3);

signal segment_n_i : std_logic_vector(0 to 7);

signal mhertz_cnt : std_logic_vector(0 to 5);

signal khertz_cnt : std_logic_vector(0 to 9);

signal hertz_cnt : std_logic_vector(0 to 9);

signal mhertz_en : std_logic;

signal khertz_en : std_logic;

signal hertz_en : std_logic;

signal slv_reg0 : std_logic_vector(0 to C_DWIDTH-1);

signal slv_reg_write_select : std_logic_vector(0 to 0);

signal slv_reg_read_select : std_logic_vector(0 to 0);

signal slv_ip2bus_data : std_logic_vector(0 to C_DWIDTH-1);

signal slv_read_ack : std_logic;

signal slv_write_ack : std_logic;

signal interrupt : std_logic_vector(0 to C_IP_INTR_NUM-1);

begin

display_ctrl(0) <= slv_reg0(0 to 7);

display_ctrl(1) <= slv_reg0(8 to 15);

display_ctrl(2) <= slv_reg0(16 to 23);

display_ctrl(3) <= slv_reg0(24 to 31);

digit_n <= digit_n_i;

segment_n <= segment_n_i;

---------------------------------------

-- Clock Dividers

---------------------------------------

GEN_1MHZ_PROCESS : process( Bus2IP_Clk ) is

begin

if Bus2IP_Clk'event and Bus2IP_Clk = '1' then

if Bus2IP_Reset = '1' then

mhertz_cnt <= (others => '0');

mhertz_en <= '0';

else

mhertz_cnt <= mhertz_cnt + 1;

if mhertz_cnt = "110010" then

mhertz_en <= '1' ;

mhertz_cnt <= (others => '0');

else

mhertz_en <= '0';

end if;

end if;

end if;

end process GEN_1MHZ_PROCESS;

GEN_1KHZ_PROCESS : process( Bus2IP_Clk ) is

begin

if Bus2IP_Clk'event and Bus2IP_Clk = '1' then

if Bus2IP_Reset = '1' then

khertz_cnt <= (others => '0');

khertz_en <= '0';

else

if mhertz_en = '1' then

khertz_cnt <= khertz_cnt + 1;

if khertz_cnt = "1111101000" then

khertz_en <= '1';

khertz_cnt <= (others => '0');

end if;

else

khertz_en <= '0';

end if;

end if;

end if;

end process GEN_1KHZ_PROCESS;

GEN_1HZ_PROCESS : process( Bus2IP_Clk ) is

begin

if Bus2IP_Clk'event and Bus2IP_Clk = '1' then

if Bus2IP_Reset = '1' then

hertz_cnt <= (others => '0');

hertz_en <= '0';

else

if khertz_en = '1' then

hertz_cnt <= hertz_cnt + 1;

if hertz_cnt = "1111101000" then

hertz_en <= '1';

hertz_cnt <= (others => '0');

end if;

else

hertz_en <= '0';

end if;

end if;

end if;

end process GEN_1HZ_PROCESS;

----------------------------------------

-- Display Update

----------------------------------------

CYC_DISP_PROCESS : process( Bus2IP_Clk ) is

begin

if Bus2IP_Clk'event and Bus2IP_Clk = '1' then

if Bus2IP_Reset = '1' then

digit_select <= (others => '0');

digit_n_i <= (others => '1');

segment_n_i <= (others => '1');

else

if khertz_en = '1' then

digit_select <= digit_select + 1;

case digit_select is

When "00" => segment_n_i <= display_ctrl(0);

digit_n_i <= "1110";

When "01" => segment_n_i <= display_ctrl(2);

digit_n_i <= "1101";

When "10" => segment_n_i <= display_ctrl(3);

digit_n_i <= "1011";

When "11" => segment_n_i <= display_ctrl(3);

digit_n_i <= "0111";

When others => null;

end case;

end if;

end if;

end if;

end process CYC_DISP_PROCESS;

slv_reg_write_select <= Bus2IP_WrCE(0 to 0);

slv_reg_read_select <= Bus2IP_RdCE(0 to 0);

slv_write_ack <= Bus2IP_WrCE(0);

slv_read_ack <= Bus2IP_RdCE(0);

-- implement slave model register(s)

SLAVE_REG_WRITE_PROC : process( Bus2IP_Clk ) is

begin

if Bus2IP_Clk'event and Bus2IP_Clk = '1' then

if Bus2IP_Reset = '1' then

slv_reg0 <= (others => '1');

else

case slv_reg_write_select is

when "1" =>

for byte_index in 0 to (C_DWIDTH/8)-1 loop

if ( Bus2IP_BE(byte_index) = '1' ) then

slv_reg0(byte_index*8 to byte_index*8+7) <= Bus2IP_Data(byte_index*8 to byte_index*8+7);

end if;

end loop;

when others => null;

end case;

end if;

end if;

end process SLAVE_REG_WRITE_PROC;

-- implement slave model register read mux

SLAVE_REG_READ_PROC : process( slv_reg_read_select, slv_reg0 ) is

begin

case slv_reg_read_select is

when "1" => slv_ip2bus_data <= slv_reg0;

when others => slv_ip2bus_data <= (others => '0');

end case;

end process SLAVE_REG_READ_PROC;

INTR_PROC : process( Bus2IP_Clk ) is

constant COUNT_SIZE : integer := 30;

constant ALL_ONES : std_logic_vector(0 to COUNT_SIZE-1) := (others => '1');

variable counter : std_logic_vector(0 to COUNT_SIZE-1);

begin

if ( Bus2IP_Clk'event and Bus2IP_Clk = '1' ) then

if ( Bus2IP_Reset = '1' ) then

counter := (others => '0');

interrupt <= (others => '0');

else

counter := counter + 1;

if ( counter = ALL_ONES ) then

interrupt <= (others => '1');

else

interrupt <= (others => '0');

end if;

end if;

end if;

end process INTR_PROC;

IP2Bus_IntrEvent(0) <= hertz_en;

IP2Bus_Data <= slv_ip2bus_data;

IP2Bus_Ack <= slv_write_ack or slv_read_ack;

IP2Bus_Error <= '0';

IP2Bus_Retry <= '0';

IP2Bus_ToutSup <= '0';

end IMP;

--------------------------------------------------------------------

MONG CÁC ANH CHỈ DẪN GIÚPgửi kèm file "import_peripheral_tutorial" và rất mong sự giúp đỡ . CÁM ƠN NHIỀU

http://www.megaupload.com/?d=7HKDLS77

... la`m ki~ tu`ng buoc set-up system cho du'ng ...

... la`m ki~ tu`ng buoc set-up system cho du'ng ...

Comment